## IBM @server BladeCenter JS20 PowerPC 970 Programming Environment

Redpaper

#### International Technical Support Organization

### IBM @server BladeCenter JS20 PowerPC 970 Programming Environment

January 2005

Note: Before using this information and the product it supports, read the information in "Notices" on page vii.

#### First Edition (January 2005)

This edition applies to the IBM @server BladeCenter JS2 and the IBM PowerPC 970 and 970FX microprocessors.

#### **Contents**

|             | Notices                                             |    |

|-------------|-----------------------------------------------------|----|

|             | Preface                                             |    |

|             | Become a published author                           |    |

| Part 1. Ove | erview of the PowerPC 970 Microprocessor            | 1  |

|             | Chapter 1. Introduction to the PowerPC 970 features |    |

|             | 1.2 Programming environment                         | 9  |

|             | 1.4 Support for 32-bit and 64-bit                   | 11 |

|             | 1.5 Register sets                                   | 14 |

|             | 1.5.2 Supervisor-level registers                    | 17 |

|             | 1.6 PowerPC instructions                            | 21 |

|             | 1.7 Superscalar and pipelining                      | 24 |

|             | 1.9 The stack frame      1.10 Parameter passing     | 31 |

|             | 1.11 Return values     1.12 Summary                 |    |

|             | Chapter 2. VMX in the PowerPC 970                   |    |

|             | 2.1.1 Vector technology review                      | 38 |

|             | 2.3 Instruction categories                          |    |

| Part 2. VMX | X programming environment                           | 51 |

|             | Chapter 3. VMX programming basics                   |    |

|             | 3.1.1 Automatic vectorization versus hand coding    | 54 |

|             | 3.1.2 Language-specific issues                      | 55 |

|             | 3.1.5 Issues and suggested remedies                 | 56 |

|             | 3.1.6 VAST code optimizer                           | 58 |

|             | 3.2 Vector data types                               | 60 |

|             | 3.4 VMX C extensions                                | 61 |

| 3.4.2 Input conversion specifications    62      3.4.3 Vector functions    64         |

|---------------------------------------------------------------------------------------|

| 3.4.4 Summary of VMX C extensions                                                     |

| Chapter 4. Application development tools                                              |

| 4.1 GNU compiler collection                                                           |

| 4.1.1 Processor-specific compiler options                                             |

| 4.1.2 Compiler options for VMX                                                        |

| 4.1.3 Suggested compiler options                                                      |

| 4.2 XL C/C++ and XL FORTRAN compiler collections                                      |

| 4.2.1 Options controlling vector code generation                                      |

| 4.2.2 Alignment-related attributes and builtins                                       |

| 4.2.3 Data dependency analysis                                                        |

| 4.2.4 Useful pragmas                                                                  |

| 4.2.5 Generating vectorization reports                                                |

|                                                                                       |

| Chapter 5. Vectorization examples                                                     |

| 5.1 Explanation of the examples                                                       |

| 5.1.1 Command-line options 85                                                         |

| 5.2 Vectorized loops                                                                  |

| 5.2.1 SAXPY example                                                                   |

| 5.2.2 Reduction loop                                                                  |

| 5.2.3 Variation of the reduction loop                                                 |

| 5.2.4 Dot product                                                                     |

| 5.2.5 Byte clamping                                                                   |

| 5.2.6 Summary 98                                                                      |

| Observe O. Assess study                                                               |

| Chapter 6. A case study                                                               |

| 6.1 Introducing vector code in your application                                       |

| 6.1.1 Appropriate uses of vectorization                                               |

| 6.1.2 Analyzing data types                                                            |

| 6.1.4 Conclusions                                                                     |

| 6.1.4 Conclusions                                                                     |

| Appendix A. Code listings                                                             |

| Code examples                                                                         |

| Code loops from Toronto Labs VAC test suite                                           |

|                                                                                       |

| Appendix B. Porting from Apple OS X                                                   |

| Compiler Flags                                                                        |

| Initialization Syntax                                                                 |

| Best Practices                                                                        |

| IBM Visual Age                                                                        |

| References                                                                            |

| Appendix C. Additional metarial                                                       |

| Appendix C. Additional material       117         Locating the Web material       117 |

| Using the Web material                                                                |

| System requirements for downloading the Web material                                  |

| How to use the Web material                                                           |

| How to use the vven material                                                          |

| Related publications                                                                  |

| IBM Redbooks                                                                          |

| Other publications                                                                    |

| Online resources                                                                      |

|       | get IE<br>rom IBI |      |      |      |  |  |  |  |  |      |  |  |      |  |  |  |  |      |      |  |  |     |

|-------|-------------------|------|------|------|--|--|--|--|--|------|--|--|------|--|--|--|--|------|------|--|--|-----|

| Index |                   | <br> | <br> | <br> |  |  |  |  |  | <br> |  |  | <br> |  |  |  |  | <br> | <br> |  |  | 121 |

#### **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

Hypervisor™

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

@server®

@server®

ibm.com®

pSeries®

AIX®

BladeCenter™

DB2®

IBM®

Lotus®

PowerOpen™

PowerPC Architecture™

PowerPC 604™

PowerPC®

POWER™

POWER3™

POWER4™ POWER5™ Redbooks™

Redbooks (logo)

Tivoli®

3890™

The following terms are trademarks of other companies:

Power MAC™ is a trademark of the Apple Computer Corporation.

AltiVec™ is a trademark of Motorola.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

Other company, product, and service names may be trademarks or service marks of others.

#### **Preface**

This Redpaper gives a broad understanding of the programming environment of the IBM® PowerPC® 970 microprocessor that is implemented in the IBM @server® BladeCenter™ JS20. It also provides information about how to take advantage of the Vector Multimedia Extensions (VMX) execution unit found in the PowerPC 970 to increase the performance of applications in 3D graphics, modelling and simulation, digital signal processing, and others.

The audience for this Redpaper is application programmers and software engineers who want to port code to the PowerPC 970 microprocessor to take advantage of the VMX performance gains.

Note: The PowerPC 970 microprocessor is available from the IBM Microelectronics Division for companies wanting to implement a PowerPC microprocessor into their embedded applications or other designs. The information in this paper will be helpful for those firmware and software engineers responsible for supporting their product. The Apple Power Mac G5 system also uses the PowerPC 970 microprocessor and application programmers can find the information within this paper useful.

#### The team that wrote this Redpaper

This Redpaper was produced by a team of specialists from around the world working at the International Technical Support Organization (ITSO), Austin Center.

**Ben Gibbs** is a Senior Consulting Engineer with Technonics, Inc. (http://www.technonics.com) in Austin, Texas. He has been involved with the POWER<sup>TM</sup> and PowerPC family of microprocessors and embedded controllers since 1989. The past seven years he has been working with the Microelectronics Division at IBM, providing training on the PowerPC embedded controllers and microprocessors. He was the project leader for this IBM Redpaper.

**Robert Arenburg** is a Senior Technical Consultant in the Solutions Enablement organization in the IBM Systems and Technology Group located in Austin, Texas, and he has worked at IBM for 13 years. He has a Ph.D. in Engineering Mechanics from Virginia Tech. His areas of expertise include high performance computing, performance, capacity planning, 3D graphics, solid mechanics, as well as computational and finite element methods.

**Damien Bonaventure** is an Advisory Software Engineer in the Toronto Software Lab. He has been with the TOBEY Optimizing backend team for seven years. His experiences include working on code generation techniques for both IBM and non-IBM systems such as Solaris and Mac OSX and implementing optimizations such as the Basis Block Instruction Scheduler for the POWER4<sup>TM</sup>. He also has experience analyzing code performance at the instruction level. He was the TOBEY team lead for the IBM XL compiler port to Mac OSX, which was the first XL compiler product to feature support for VMX. He holds a Bachelor of Applied Science in Computer Engineering from the University of Toronto.

**Bradley Elkin** is a Senior Software Engineer for IBM. He holds a Ph.D. in Chemical Engineering from the University of Pennsylvania and has 17 years of experience in high performance computing. His areas of expertise include applications from computational fluid mechanics, computational chemistry, and bioinformatics. He has written several articles for IBM @server Development Domain.

**Rogeli Grima** is a research staff member at the CEPBA IBM Research Institute in Spain. He has three years of experience in applied mathematics. He has also collaborated on the development of JS20 blade server solution for bioinformatics.

Amy Wang obtained her Bachelor of Applied Science degree in 1999, specializing in Computer Engineering offered under the Engineering Science faculty at the University of Toronto. In the fall of 2001, she completed her Master of Applied Science degree in Computer Engineering at the University of Toronto. In 2002, she joined the IBM Toronto Software Lab, contributing her skills to the development of various compiler backend optimizations. Currently, she is working with the IBM Watson research team to implement automatic simdization, which will enable automatic VMX code generation for the JS20 hardware.

Thanks to the following people for their contributions to this project:

Chris Blatchley, Lupe Brown, Arzu Gucer, and Scott Vetter ITSO, Austin Center

Omkhar Arasaratnam IBM Toronto Canada

James Kelly IBM Melbourne Australia

Randy Swanberg IBM Austin

#### Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook dealing with specific products or solutions, while getting hands-on experience with leading-edge technologies. You'll team with IBM technical professionals, Business Partners or customers.

Your efforts will help increase product acceptance and customer satisfaction. As a bonus, you'll develop a network of contacts in IBM development labs, and increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our papers to be as helpful as possible. Send us your comments about this Redpaper or other Redbooks™ in one of the following ways:

► Use the online **Contact us** review redbook form found at:

ibm.com/redbooks

Send your comments in an email to:

redbook@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. JN9B Building 905 11501 Burnet Road Austin, Texas 78758-3493

#### Part 1

# Overview of the PowerPC 970 Microprocessor

This section reviews the PowerPC 64-bit architecture as it applies to the PowerPC 970 microprocessor. Chapter 1 describes the features, instructions, instruction pipelines, programming environment, data types, register sets, and application binary interface specification. Chapter 2 focuses on the Vector Multimedia Extension (VMX) implementation in the PowerPC 970 and includes a discussion of VMX technology, instruction categories, and memory addressing.

## 1

## Introduction to the PowerPC 970 features

The IBM PowerPC 970 Reduced Instruction Set Computer (RISC) microprocessor is an implementation of the PowerPC Architecture™. This chapter provides an overview of the PowerPC 970 features, including a block diagram showing the major functional components. It also provides information about how 970 implementation complies with the PowerPC architecture definition.

**Note:** This paper uses the term *PowerPC 970* to refer to both the IBM PowerPC 970 and IBM PowerPC 970FX microprocessors. Also, it uses the term *JS20 blade* to refer to the IBM @server BladeCenter JS20.

**Fact:** Altvec is used by Motorola, Velocity Engine is used by Apple, and VMX is used by IBM to refer to the PowerPC vector execution unit such as the one implemented in the PowerPC 970 microprocessor.

#### 1.1 Overview

The PowerPC 970 is a 64-bit PowerPC RISC microprocessor with VMX extensions. VMX extensions are single-instruction, multiple-data (SIMD) operations that accelerate data intensive processing tasks. This processor is designed to support multiple system configurations ranging from desktop and low-end server applications uniprocessor up through a 4-way simultaneous multiprocessor (SMP). The JS20 blades use the PowerPC 970 in a 2-way SMP configuration.

The PowerPC 970 is comprised of three main components:

- ▶ PowerPC 970 core, which includes VMX execution units

- ▶ PowerPC 970 storage (STS), which includes core interface logic, non-cacheable unit, L2 cache and controls, and the bus interface unit

- ▶ 970 Pervasive functions

The PowerPC 970 microprocessor consists of the following features:

- ► 64-bit implementation of the PowerPC AS Architecture (version 2.0)

- Binary compatibility for all PowerPC AS application level code (problem state)

- Binary compatibility for all PowerPC application level code (problem state)

- N-1 operating system capable for AIX® and Linux

- Support for 32-bit operating system bridge facility

- Vector/SIMD Multimedia Extension (VMX)

- Layered implementation strategy for very high frequency operation

- 64 KB direct-mapped instruction cache

- 128 byte cache lines

- Deeply pipelined design

- Fetch of eight instructions on eight-word boundaries per cycle

- 16 stages for most fixed-point register-register operations

- 18 stages for most load and store operations (assuming L1 Dcache hit)

- 21 stages for most floating point operations

- 19, 22, and 25 stages for fixed-point, complex-fixed, and floating point operations, respectively in the VALU.

- 19 stages for VMX permute operations

- Dynamic instruction cracking for some instructions allows for simpler inner core dataflow

- · Dedicated dataflow for cracking one instruction into two internal operations

- Microcoded templates for longer emulation sequences

- ► Speculative superscalar inner core organization

- Aggressive branch prediction

- · Scan all eight fetched instructions for branches each cycle

- Predict up to two branches per cycle (if the first one is predicted fall-through)

- 32-entry count cache for address prediction (indexed by address of bcctr instructions)

- Support for up to 16 predicted branches in flight

- Prediction support for branch direction and branch addresses

- In order dispatch of up to five operations into distributed issue queue structure

- Out of order issue of up to 10 operations into 10 execution pipelines

- Two load or store operations

- Two fixed-point register-register operations

- Two floating-point operations

- · One branch operation

- One condition register operation

- One VMX permute operation

- One VMX ALU operation

- Capable of restoring the machine state for any of the instructions in flight

- Very fast restoration for instructions on group boundaries (that is, branches)

- Slower for instructions contained within a group

- Register renaming on GPRs, FPRs, VRFs, CR Fields, XER (parts), FPSCR, VSCR, Link and Count

- 80-entry GPR rename mapper (32 architected GPRs plus four eGPRs)

- 80-entry FPR rename mapper (32 architected FPRs)

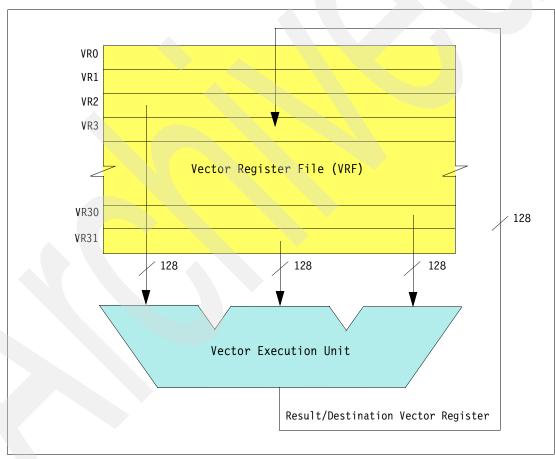

- 80-entry VRF rename mapper (32 architected VRFs)

- 24-entry XER rename mapper (XER broken into four mappable fields and one non-mappable)

- Mappable fields: ov, ca/oc, fxcc, tgcc

- Non-mappable bits: dc, ds, string-count, other\_bits

- Special fields (value predict): so

- 16-entry LR/CTR rename mapper (one LR and one CTR)

- 32-entry CR rename mapper (eight CR fields plus one eCR field)

- 20-entry FPSCR rename mapper

- No register renaming on: MSR, SRR0, SRR1, DEC, TB, HID0, HID1, HID4, SDR1, DAR, DSISR, CTRL, SPRG0, SPRG1, SPRG2, SPRG3, ASR, PVR, PIR, SCOMC, SCOMD, ACCR, CTRL, DABR, VSCR, or PerfMon registers

- Instruction queuing resources:

- Two, 18-entry issue queues for fixed-point and load/store instructions

- Two, 10-entry issue queues for floating-point instructions

- 12-entry issue queue for branches instructions

- 10-entry issue queue for CR-logical instructions

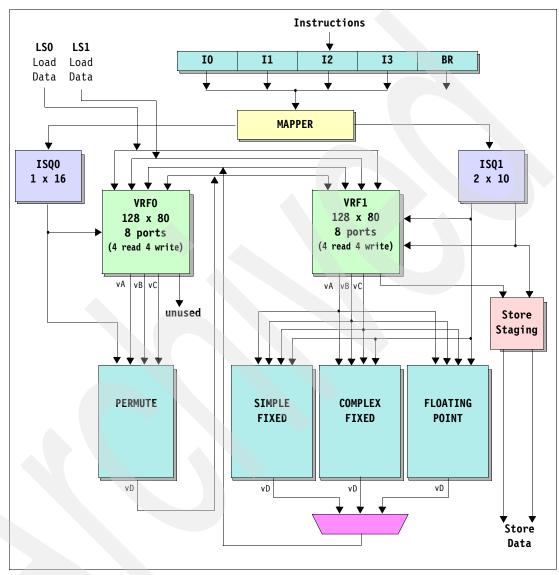

- 16-entry issue queue for Vector Permute instructions

- 20-entry issue gueue for Vector ALU instructions and VMX Stores

- ► Large number of instructions in flight (theoretical maximum of 215 instructions)

- Up to 16 instructions in instruction fetch unit (fetch buffer and overflow buffer)

- Up to 32 instructions in instruction fetch buffer in instruction decode unit

- Up to 35 instructions in three decode pipe stages and four dispatch buffers

- Up to 100 instructions in the inner-core (after dispatch)

- Up to 32 stores queued in the STQ (available for forwarding)

- Fast, selective flush of incorrect speculative instructions and results

- Vector Multimedia eXtension (VMX) execution pipelines

- Two dispatchable units:

- · VALU contains three subunits:

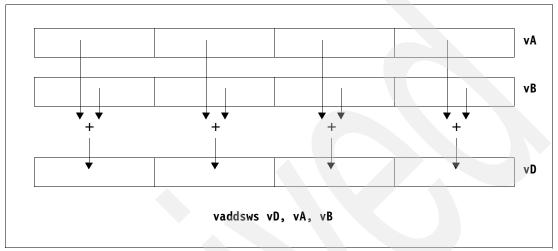

Vector simple fixed: 1-stage execution

Vector complex fixed: 4-stage execution

Vector floating point: 7-stage execution

- VPERM 1-stage execution

- Out-of-order issue with bias towards oldest operations first

- Symmetric forwarding between the permute and VALU pipelines

- Specific focus on storage latency management

- 32 KB, two-way set associative data cache

- 128 byte cache line, FIFO replacement policy

- Triple ported to support two reads and one write every cycle

- Two cycle load-to-use (cycles between load instruction and able to used by dependent structure) penalty for FXU loads

- Four cycle load-to-use penalty for FPU loads

- Three cycle load-to-use penalty for VMX VPERM loads

- Four cycle load-to-use penalty for VMX VALU loads

- Out-of-order and speculative issue of load operations

- Support for up to eight outstanding L1 cache line misses

- Hardware initiated instruction prefetching from L2 cache

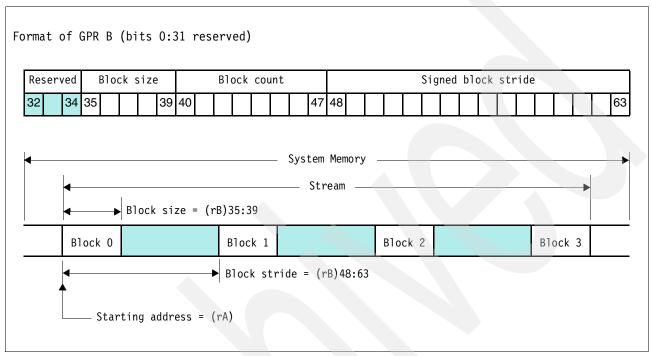

- Software initiated data stream prefetching with support for up to eight active streams

- Critical word forwarding and critical sector first

- New branch processing and prediction hints for branch instructions

#### ▶ L2 Cache Features

- 512KB size, eight-way set associative

- Fully inclusive of L1 data cache

- Unified L2 cache controller (instructions, data, page table entries, and so on)

- Store-in L2 cache (store-through L1 cache)

- Fully integrated cache, tags, and controller

- Five-state modified, exclusive, recent, shared, and invalid (MERSI) coherency protocol

- Runs at core frequency (1:1)

- Handle all cacheable loads/stores (including lwarx/stcwx)

- Critical octaword forwarding on data loads

- Critical octaword forwarding in instruction fetches

#### Power management

- Doze, nap, and deep nap capabilities

- Static power management

- · Software initiated doze and nap mode

- Dynamic power management

- · Parts of the design stop their (hardware initiated) clocks when not in use

- PowerTune

- Software initiated slow down of the processor; selectable to half or quarter of the nominal operating frequency

- Storage Subsystem (STS)

- Encompasses the Core Interface Unit, Non-Cachable Unit (NCU), the L2 cache controller and 512KB L2 cache, and the Bus Interface Unit (BIU)

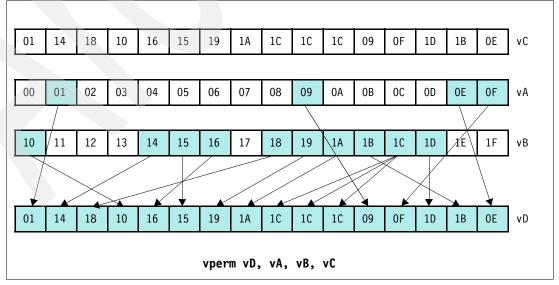

PowerPC 970 Core 64KB Instruction Instruction Instruction Decode Unit Fetch Unit Cache Dispatch Buffer Global Completion Register Maps - GPR, FPR, VRF, CR, CTR, LK Table VMX ALU FX2/LSU2 FPUVMX Permute FX1/LSU1 CR $\mathsf{BR}$ Issue Queue LS2 BR FP1 FP2 **VPERM** VALU FX1 LS1 FX2 CR32KB Data Cache CTR/LK FPR VRF VRF **GPR** GPR CR RF STS Core Interface Unit L2 Dir/Cntl NCU 512KB L2 Cache Bus Interface Unit PowerPC 970 Bus

Figure 1-1 shows the block diagram of the PowerPC 970 core.

Figure 1-1 PowerPC 970 block diagram

#### 1.2 Programming environment

The programming environment consists of the resources that are accessible from the processor running in problem state mode (non-supervisory), which is called *user mode* by the operating system.. The PowerPC architecture is a load-store architecture that defines specifications for both 32-bit and 64-bit implementations. The PowerPC 970 is a 64-bit implementation. The instruction set is partitioned into four functional classes: branch, fixed-point, floating-point, and VMX.

The registers are also partitioned into groups corresponding to these classes. That is, there are condition code and branch target registers for branches, floating-point registers for floating-point operations, general-purpose registers for fixed-point operations, and vector registers for VMX operations.

This partition benefits superscalar implementations by reducing the interlocking necessary for dependency checking. The explicit indication of all operands in the instructions, combined with the partitioning of the PowerPC architecture into functional classes, exposes dependences to the compiler. Although instructions must be word (32-bit) aligned, data can be misaligned within certain implementation-dependent constraints.

The floating-point facilities support compliance to the IEEE 754 Standard for Binary Floating-Point Arithmetic (IEEE 754).

In 64-bit implementations, such as the PowerPC 970, two modes of operation are determined by the 64-bit mode (SF) bit in the Machine State Register: 64-bit mode (SF set to 1) and 32-bit mode (SF cleared to 0), for compatibility with 32-bit implementations. Application code for 32-bit implementations executes without modification on 64-bit implementations running in 32-bit mode, yielding identical results. All 64-bit implementation instructions are available in both modes. Identical instructions, however, can produce different results in 32-bit and 64-bit modes. Differences between 32-bit and 64-bit mode include but are not limited to:

#### Addressing

Although effective addresses in 64-bit implementations have 64 bits, in 32-bit mode, the high-order 32 bits are ignored during data access and set to zero during instruction fetching. This modification of the high-order bits of the address might produce an unexpected jump following the transition from 64-bit mode to 32-bit mode.

#### Status bits

The register result of arithmetic and logical instructions is independent of mode, but setting of status bits depends on the mode. In particular, recording, carry-bit—setting, or overflow-bit—setting instruction forms write the status bits relative to the mode. Changing the mode in the middle of a code sequence that depends on one of these status bits can lead to unexpected results.

#### ▶ Count Register

The entire 64-bit value in the Count Register of a 64-bit implementation is decremented, even though conditional branches in 32-bit mode only test the low-order 32 bits for zero.

#### 1.3 Data types

The PowerPC 64-bit architecture supports the data types shown in Table 1-1. The basic data types are byte (8-bit), halfword (16-bits), word (32-bits), and doubleword (64-bits) for fixed-point operations. The floating-point types are single-precision (32-bits) and double-precision (64-bits). Vector data types are quadwords (128-bits).

Table 1-1 PowerPC 64-bit data types

| ANSI C                               | Size<br>(bytes)                                                                                                                                                                                                                                                                                                                              | Alignment                                                                                                                                                                                                                  | PowerPC                   |  |  |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|--|

| _bool                                | 1                                                                                                                                                                                                                                                                                                                                            | byte                                                                                                                                                                                                                       | unsigned byte             |  |  |  |  |  |  |  |

| char<br>unsigned char                | 1                                                                                                                                                                                                                                                                                                                                            | byte                                                                                                                                                                                                                       | unsigned byte             |  |  |  |  |  |  |  |

| signed char                          | 1                                                                                                                                                                                                                                                                                                                                            | byte                                                                                                                                                                                                                       | signed byte               |  |  |  |  |  |  |  |

| short<br>signed short                | 2                                                                                                                                                                                                                                                                                                                                            | halfword                                                                                                                                                                                                                   | signed halfword           |  |  |  |  |  |  |  |

| unsigned short                       | 2                                                                                                                                                                                                                                                                                                                                            | halfword                                                                                                                                                                                                                   | unsigned halfword         |  |  |  |  |  |  |  |

| int<br>signed int<br>enum            | 4                                                                                                                                                                                                                                                                                                                                            | word                                                                                                                                                                                                                       | signed word               |  |  |  |  |  |  |  |

| unsigned int                         | 4                                                                                                                                                                                                                                                                                                                                            | word                                                                                                                                                                                                                       | unsigned word             |  |  |  |  |  |  |  |

| long int<br>signed long<br>long long | 8                                                                                                                                                                                                                                                                                                                                            | doubleword                                                                                                                                                                                                                 | signed doubleword         |  |  |  |  |  |  |  |

| unsigned long<br>unsigned long long  | 8                                                                                                                                                                                                                                                                                                                                            | doubleword                                                                                                                                                                                                                 | unsigned doubleword       |  |  |  |  |  |  |  |

| int128_t                             | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | signed quadword           |  |  |  |  |  |  |  |

| unit128_t                            | 16                                                                                                                                                                                                                                                                                                                                           | doubleword                                                                                                                                                                                                                 | unsigned quadword         |  |  |  |  |  |  |  |

| any *<br>any (*) ()                  | 8                                                                                                                                                                                                                                                                                                                                            | doubleword                                                                                                                                                                                                                 | unsigned doubleword       |  |  |  |  |  |  |  |

| float                                | 4                                                                                                                                                                                                                                                                                                                                            | word                                                                                                                                                                                                                       | single precision          |  |  |  |  |  |  |  |

| double                               | 8                                                                                                                                                                                                                                                                                                                                            | doubleword                                                                                                                                                                                                                 | double precision          |  |  |  |  |  |  |  |

| long double                          | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | extended precision        |  |  |  |  |  |  |  |

| 16*char                              | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of signed bytes    |  |  |  |  |  |  |  |

| 16*unsigned char                     | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of unsigned bytes  |  |  |  |  |  |  |  |

| 8*short                              | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of signed shorts   |  |  |  |  |  |  |  |

| 8*unsigned short                     | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of unsigned shorts |  |  |  |  |  |  |  |

| 4*int                                | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of signed words    |  |  |  |  |  |  |  |

| 4*unsigned int                       | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of unsigned words  |  |  |  |  |  |  |  |

| 4*float                              | 16                                                                                                                                                                                                                                                                                                                                           | quadword                                                                                                                                                                                                                   | vector of floats          |  |  |  |  |  |  |  |

|                                      | char unsigned char signed char short signed short unsigned short int signed int enum unsigned int long int signed long long long unsigned long unsigned long long unsigned long long dunsigned long long int128_tunit128_t any * any (*) () float double long double 16*char 16*unsigned char 8*short  8*unsigned short 4*int 4*unsigned int | _bool 1 char unsigned char 1 short signed short 2 int signed int enum 4 long int signed long long long long long unsigned long long unsigned long long unsigned long long unsigned long long long long long long long long | _bool                     |  |  |  |  |  |  |  |

In Table 1-1 on page 10, extended precision is the AIX 128-bit long double format composed of two double-precision numbers with different magnitudes that do not overlap. The high-order double-precision value (the one that comes first in storage) must have the larger magnitude. The value of the extended-precision number is the sum of the two double-precision values and include the following features:

- ► Extended precision provides the same range of double precision (about 10\*\*(-308) to 10\*\*308) but more precision (a variable amount, about 31 decimal digits or more).

- As the absolute value of the magnitude decreases (near the denormal range), the precision available in the low-order double also decreases.

- ► When the value represented is in the denormal range, this representation provides no more precision than 64-bit (double) floating point.

- ► The actual number of bits of precision can vary. If the low-order part is much less then 1 ULP of the high-order part, significant bits (either all 0's or all 1's) are implied between the significands of high-order and low-order numbers. Some algorithms that rely on having a fixed number of bits in the significand can fail when using extended precision.

This extended precision differs from the IEEE 754 in the following ways:

- Software support is restricted to round-to-nearest mode. Programs that use extended precision must ensure that this rounding mode is in effect when extended-precision calculations are performed.

- ► The software does not fully support the IEEE special numbers not-a-number and INF. These values are encoded in the high-order double value only. The low-order value is not significant.

- ► The software does not support the IEEE status flags for overflow, underflow, and other conditions. These flags have no meaning in this format.

#### 1.4 Support for 32-bit and 64-bit

The PowerPC 970 uses the same data paths and execution units for both 32-bit and 64-bit operations. There are no limitations or reduced performance situations due to running applications in 32-bit mode. There is no "compatibility" or "emulation" mode. Whether the processor is in 32-bit mode or 64-bit mode is controlled by the MSR[SF] bit. (See Table 1-2 on page 17 for a description of the machine state register.)

The PowerPC architecture was defined from the beginning to be a 64-bit architecture and the 32-bit implementations of the PowerPC architecture are subsets. For example, the PowerPC 604e microprocessor implemented in the IBM pSeries® 43P-150 workstation is a 32-bit PowerPC microprocessor. This microprocessor can execute all the instructions in the PowerPC architecture except those that involve the doubleword (64-bit) operands such as 1d (load doubleword). Nothing would prevent the operating system from trapping and emulating these 64-bit instructions, being completely transparent to the application. Another example of this is the 1wz (load word and zero) instruction.

On the PowerPC 970, a 32-bit word is loaded from memory into the instruction-specified 64-bit general-purpose register and the upper 32-bits of the register are set to zero (cleared). On the PowerPC 604e the same instruction is executed, and the same word loaded into the same register. However, there is nothing to zero because the register is 32-bits on this microprocessor. For the most part, binary compatibility exists between the 32-bit and 64-bit PowerPC microprocessors. When it becomes time for a customer to migrate their applications from 32-bit IBM @server pSeries systems to the 64-bit IBM @server BladeCenter JS20, the porting effort can be minimal. This cannot be said for many other architectures today.

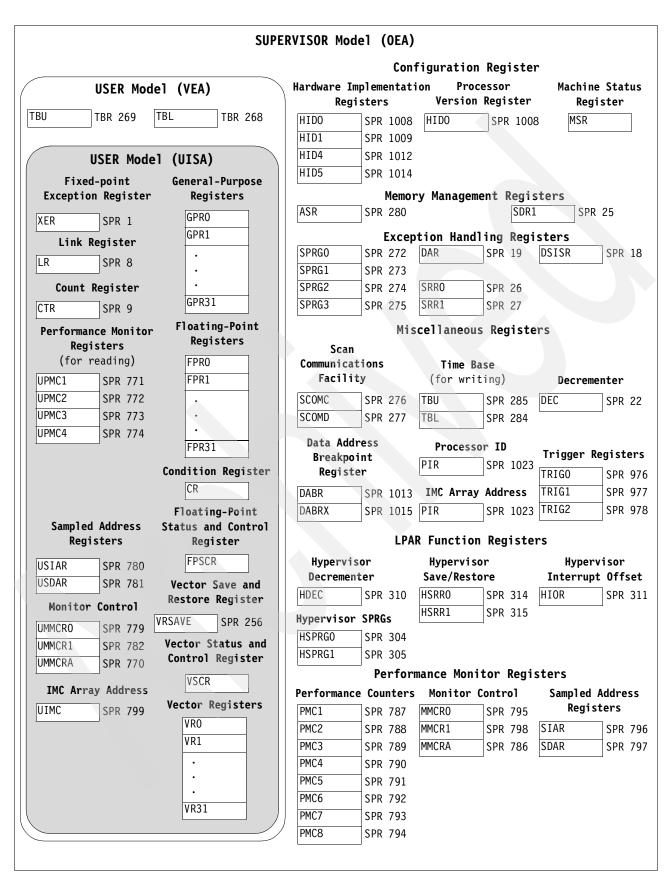

#### 1.5 Register sets

Registers are defined at all three levels of the PowerPC architecture, namely user instruction set architecture (UISA), virtual environment architecture (VEA), and operating environment architecture (OEA). The PowerPC architecture defines register-to-register operations for all computational instructions. Source data for these instructions are accessed from the on-chip registers or are provided as immediate values embedded in the opcode. The three-register instruction format allows specification of a target register distinct from the two source registers, thus preserving the original data for use by other instructions and reducing the number of instructions required for certain operations. Data is transferred between memory and registers with explicit load and store instructions only. Figure 1-2 on page 13 shows the registers found in the PowerPC 970.

PowerPC processors have two levels of privilege: supervisor mode of operation (typically used by the operating system) and user mode of operation (used by the application software, it is also called *problem state*).

The programming models incorporate 32 general-purpose registers, 32 floating-point registers, 32 vector registers, special-purpose registers, and several miscellaneous registers. Each PowerPC microprocessor also has its own unique set of hardware implementation-dependent (HID) registers.

While running in supervisor mode. the operating system is able to execute all instructions and access all registers defined in the PowerPC Architecture. In this mode, the operating system establishes all address translations and protection mechanisms, loads all processor state registers. and sets up all other control mechanisms defined on the 970 processor. While running in user mode (problem state), many of these registers and facilities are not accessible, and any attempt to read or write these register results in a program exception.

Figure 1-2 Registers in the PowerPC 970

#### 1.5.1 User-level registers

The user-level registers can be accessed by all software with either user or supervisor privileges and include the following registers:

- General-purpose registers (GPRs). The thirty-two 64-bit GPRs (GPR0–GPR31) serve as data source or destination registers for integer instructions and provide data for generating addresses.

- ► Floating-point registers (FPRs). The thirty-two 64-bit FPRs (FPR0–FPR31) serve as the data source or destination for all floating-point instructions.

- Condition register (CR). The 32-bit CR consists of eight 4-bit fields (CR0–CR7) that reflect results of certain arithmetic operations and provide a mechanism for testing and branching.

- ► Floating-point status and control register (FPSCR). The FPSCR contains all floating-point exception signal bits, exception summary bits, exception enable bits, and rounding control bits that are needed for compliance with the IEEE 754.

- Vector registers (VRs). The VR file consists of thirty-two 128-bit VRs (VR0-VR31). The VRs serve as vector source and vector destination registers for all vector instructions.

- Vector status and control register (VSCR). The VSCR contains the non-Java and saturation bit. The remaining bits are reserved.

- Vector save and restore register (VRSAVE). The VRSAVE assists the application and operating system software in saving and restoring the architectural state across context-switched events.

The remaining user-level registers are special purpose registers (SPRs). The PowerPC architecture provides a separate mechanism for accessing SPRs (the mtspr and mfspr instructions). These instructions are commonly used to explicitly access certain registers, while other SPRs can be accessed more typically as the side effect of executing other instructions.

For a detailed description of the GPRs, FPRs, CR, and FPSCR, consult *PowerPC Microprocessor Family: The Programming Environments* available at either of the following Web addresses:

```

http://www.chips.ibm.com

http://www.technonics.com/powerpc/publications

```

For information about the VRs, see PowerPC Microprocessor Family: AltiVec Technology Programming Environments, also available at these addresses.

#### 1.5.2 Supervisor-level registers

The PowerPC OEA defines the registers that an operating system uses for memory management, configuration, exception handling, and other operating system functions.

The OEA defines the following supervisor-level registers for 32-bit implementations:

- Configuration registers

- Machine state register (MSR). The MSR defines the state of the processor. The MSR can be modified by the Move to Machine State Register (mtmsr) System Call (sc) instructions and the Return from Exception (rfi) instruction. The MSR can be read by the Move from Machine State Register (mfmsr) instruction. When an exception is taken, the contents of the MSR are saved to the machine status save and restore register 1 (SRR1), described in the bulleted list that follows.

For information about the MSR, see the *PowerPC Microprocessor Family: The Programming Environments* manual available either of the following Web addresses:

```

http://www.chips.ibm.com

http://www.technonics.com/powerpc/publications

```

**Important:** The MSR is defined by the PowerPC architecture. However, the bit definitions can change from one PowerPC microprocessor type to another. The PowerPC 970 user's manual describes the actual bit implementation of the MSR.

Processor version register (PVR). The PVR is a read-only register that identifies the version (model) and revision level of the PowerPC processor. For more information, refer to the PowerPC 970 datasheet. The processor revision level (PVR[16:31]) starts at x'0100', indicating revision '1.0'. As revisions are made, bits [29:31) indicate minor revisions. Similarly, bits [20:23] indicate major changes. Bits [16:19] are a technology indicator. Bits [24:27] are reserved for future use.

**Note:** The processor version number (PVR[0:15]) for the PowerPC 970 is 0x0039. In future versions of the PowerPC 970, this section of the version number will only change if there are significant software-visible changes in the design.

#### Memory management registers

- Address space register (ASR). In the PowerPC 970, the ASR is supported and is considered a hypervisor resource. Due to the software reload of the SLBs on the 970FX, this register does not actually participate in any other specific hardware functions on the chip. It has been included as a convenience (and performance enhancement) for the SLB reload software.

- Storage description register (SDR1). The SDR1 holds the page table base address used in virtual-to-physical address translation.

#### Exception-handling registers

- Data address register (DAR). After a DSI or an alignment exception, the DAR is set to the effective address generated by the faulting instruction.

- Software use SPRs (SPRG0–SPRG3). SPRG0–SPRG3 are provided for operating system use. These registers are not architecturally defined and also are not found in all POWER and PowerPC microprocessors. They might or might not be used by the operating system. Their ideal use is for servicing interrupts and used as scratch pad registers. The point here is that level-0 storage (registers) are faster to access than level-1 storage (L1 cache), level-2 storage (L2 caches), and so on.

- Data storage interrupt status register (DSISR). The bits in the DSISR reflect the cause of DSI and alignment exceptions.

- Machine status save and restore register 0 (SRR0). The SRR0 is used to save the address of the instruction at which normal execution resumes when the rfi instruction executes at the end of an exception handler routine.

- Machine status save and restore register 1 (SRR1). The SRR1 is a 64-bit register used to save machine status on exceptions and restore machine status register when an rfid instruction is executed. In the 970FX, bits [2], [4:32], [34], [37-41], [57], [60], and [63] are treated as reserved. These bits are not implemented and return the value 0b0 when read.

#### ► Miscellaneous registers

- Time base (TB). The TB is a 64-bit structure provided for maintaining the time of day and operating interval timers. The TB consists of two 32-bit registers: time base upper (TBU) and time base lower (TBL). The time base registers can be written to only by supervisor-level software but can be read by both user and supervisor-level software.

- Decrementer register (DEC). The DEC is a 32-bit decremented counter that provides a

mechanism for causing a decrementer exception after a programmable delay; the

frequency is a subdivision of the processor clock.

- Data address breakpoint register (DABR). The DABR register is used to cause a breakpoint exception if a specified data address is encountered.

- Processor ID register (PIR). The PIR is used to differentiate between individual processors in a multiprocessor environment.

#### PowerPC 970-specific registers

The PowerPC architecture allows implementation-specific SPRs. Those incorporated in the PowerPC 970 are described as follows.

- Instruction address breakpoint (IABR). The PowerPC 970 does not support a software visible form of the instruction address breakpoint facility. As a debug feature that is accessible via the support processor interface, it does support an instruction breakpoint feature.

- Hardware implementation-dependent register 0 (HID0). The HID0 controls various functions, such as enabling checkstop conditions, and locking, enabling, and invalidating the instruction and data caches, power modes, miss-under-miss, and others. This register is hypervisor write access and privileged read access only.

- Hardware implementation-dependent register 1 (HID1). The HID1 contains additional mode bits that are related to the instruction fetch and instruction decode functions in the PowerPC 970. This register is hypervisor write access and privileged read access only.

- Hardware implementation-dependent register 4 (HID4) and hardware implementation-dependent register 5 (HID5). The HID4 and HID5 contain bits related to LPAR and the load-store function in the PowerPC 970. All of these registers are hypervisor write access and privileged read access only.

- Performance monitor registers. The following registers are used to define and count events for use by the performance monitor:

- The performance monitor counter registers (PMC1-PMC8) are used to record the number of times a certain event has occurred. UPMC1-UPMC8 provide user-level read access to these registers.

- The monitor mode control registers (MMCR0, MMCR1, MMCRA) are used to enable various performance monitor interrupt functions. UMMCR0, UMMCR1, UMMCRA provide user-level read access to these registers.

- The sampled instruction address register (SIAR) contains the effective address of an instruction executing at or around the time that the processor signals the performance monitor interrupt condition.

- The sampled data address register (SDAR) contains the effective address of the storage access instruction.

**Note:** While it is not guaranteed that the implementation of PowerPC 970-specific registers is consistent among PowerPC processors, other processors can implement similar or identical registers.

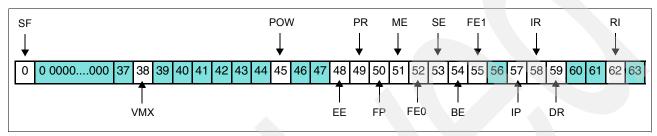

#### 1.5.3 Machine state register

The machine state register (MSR) is a 64-bit register on 64-bit PowerPC implementations and a 32-bit register in 32-bit PowerPC implementations. The MSR on the PowerPC 970 is a 64-bit register. The MSR defines the state of the processor. When an exception occurs, the contents of the MSR register are saved in SRR1 or, when a hypervisor interrupt occurs, are saved in HSRR1. A new set of bits are loaded into the MSR as determined by the exception. The MSR can also be modified by the mtmsrd (or mtmsr), sc, rfid or hrfid instructions. It can be read by the mfmsr instruction.

Figure 1-3 shows the format of this register. Table 1-2 describes the bits. Bits 1 through 37, 39 through 44, 46, 47, 56, 60, 61, and 63 are reserved bits and return 0b0 when read.

Figure 1-3 Machine State Register (MSR)

Table 1-2 MSR bit settings

| Bit   | Name | Description                                                                                                                                                                 |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | SF   | Sixty-four bit mode  O The processor runs in 32-bit mode  1 The processor runs in 64-bit mode                                                                               |

| 1:37  |      | Reserved bits                                                                                                                                                               |

| 38    | VMX  | VMX execution unit enable  0 VMX execution unit disabled  1 VMX execution enabled                                                                                           |

| 39:44 |      | Reserved bits                                                                                                                                                               |

| 45    | POW  | Power management enable O Power management disabled (normal operation mode) 1 Power management enabled (reduced power mode)                                                 |

| 46:47 |      | Reserved bits                                                                                                                                                               |

| 48    | EE   | External interrupt enable  O Processor is not preempted by external interrupts or decrementer  1 Processor is enabled to take external and decremeter interrupts            |

| 49    | PR   | Privilege level (Problem state mode)  O Processor is in supervisory mode (AIX or Linux kernel/system mode)  1 Processor is in non-supervisory mode (AIX or linux user mode) |

| 50    | FP   | Floating-point enable  O Floating-point execution unit is disabled  1 Floating-point execution unit is enabled                                                              |

| 51    | ME   | Machine check enable  O Machine check exceptions are disabled  1 Machine check exceptions are enabled                                                                       |

| Bit   | Name | Description                                                                                                                                                                                                                                                                                                                                       |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52    | FEO  | Floating-point exception mode 0 Used with bit 55 (FE1) to: FEO FE1 Mode  0 0 Floating-point exceptions are disabled 0 1 Floating-point imprecise nonrecoverable 1 0 Floating-point imprecise recoverable 1 1 Floating-point precise mode                                                                                                          |

| 53    | SE   | Single-step trace enable  O The processor executes instructions normally  The processor generates a single-step trace exception (debugging)                                                                                                                                                                                                       |

| 54    | BE   | Branch trace enable  O The processor executes branch instructions normally  The processor generates a branch trace exception at the completion of a branch instruction, regardless of whether the branch was taken                                                                                                                                |

| 55    | FE1  | Floating-point exception mode 1 See bit 52 (FEO) for details                                                                                                                                                                                                                                                                                      |

| 56    |      | Reserved bit                                                                                                                                                                                                                                                                                                                                      |

| 57    | IP   | Interrupt prefix  0 Interrupts are vectored to the real address of 0x0000_0000_000n_nnnn  1 Interrupts are vectored to the real address of 0xFFFF_FFFF_FFFn_nnnn  Note: This bit is automatically set (1) during reset and then cleared (0) by firmware after the operating system has been loaded relative to real address 0x0000_0000_0000_0000 |

| 58    | IR   | Instruction address translation  O Instruction address translation is disabled (real mode)  1 Instruction address translation is enabled (virtual mode)                                                                                                                                                                                           |

| 59    | DR   | Data address translation  O Data address translation is disabled (real mode)  1 Data address translation is enabled (virtual mode)                                                                                                                                                                                                                |

| 60:61 |      | Reserved bits                                                                                                                                                                                                                                                                                                                                     |

| 62    | RI   | Recoverable exception  0 Exception is not recoverable  1 Exception is recoverable                                                                                                                                                                                                                                                                 |

| 63    |      | Reserved bit                                                                                                                                                                                                                                                                                                                                      |

The default state of this register coming out of reset is that all the bits of the MSR are cleared except bits 0 (SF) and 57 (IP) which are set to one (1). Therefore, the PowerPC 970 begins in 64-bit mode and fetches the first instruction from 0xFFFF\_FFF\_FFF0\_0100 (system reset vector).

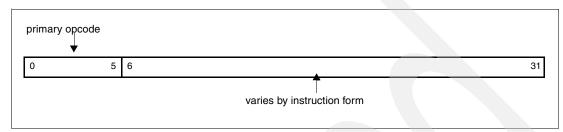

#### 1.6 PowerPC instructions

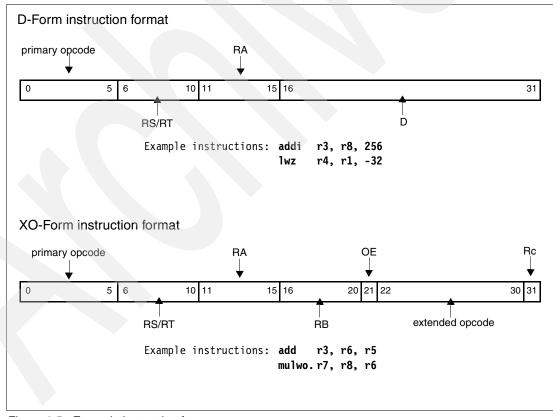

All instructions in the PowerPC architecture are 32-bits. This is typical of a reduced instruction set computer (RISC) architecture. Figure 1-4 shows the basic format of a PowerPC instruction. The left most six bits (0-5) are the primary opcode. The remaining 26 bits can take 15 different forms.

Figure 1-4 PowerPC instruction format

The PowerPC architecture describes the following forms: A-form, B-form, D-form, DS-form, I-form, M-form, MDS-form, SC-form, X-form, XFL-form, XFX-form, XL-form, XO-form, and the XS-form.

Figure 1-5 shows an example comparison between the D-form and the XO-form.

Figure 1-5 Example instruction forms

In Figure 1-5 on page 19, the instruction addi r3, r8, 256 has:

- ▶ Bits 0 through 5 encoded with the bit value of 0b001110 (14) as the primary opcode.

- ▶ Bits 6 through 10 encoded with 0b00011 (3) for GPR 3.

- ▶ Bits 11 through 15 encoded with 0b01000 (8) for GPR 8.

- ▶ Bits 16 through 31 contain 0b0000000100000000 (256), a 16-bit signed two's complement integer that is extended to 64 bits during execution.

During the execution of this instruction, the contents of GPR 8 are added to 256 and the results placed into GPR 3.

The instruction 1wz r4, r3, -32 has:

- ▶ Bits 0 through 5 encoded with the bit value of 0b100000 (32) as the primary opcode.

- ▶ Bits 6 through 10 encoded with 0b00100 (4) for GPR 4.

- ▶ Bits 11 through 15 encoded with 0b00001 (1) for GPR 1.

- ▶ Bits 16 through 31 contain 0b11111111111100000 (-32), a 16-bit signed two's complement integer that is extended to 64 bits during execution.

During the execution of this instruction, the contents of GPR 1 are added to the immediate value (-32) to form the effective address.

If address translation is enabled (MSR[DR] = 1), the effective address is translated to a real address and the 32-bit word at that address is placed into GPR 4, along with the upper 32-bits of the 64-bit GPR that is set to zero. If address translation is disabled (MSR[DR] = 0), the effective address is the real address, and no translation occurs.

The instruction add r3, r6, r5 has:

- ▶ Bits 0 through 5 encoded with the bit value of 0b011111 (31) as the primary opcode.

- ▶ Bits 6 through 10 encoded with 0b00011 (3) for GPR 3.

- ▶ Bits 11 through 15 encoded with 0b00110 (6) for GPR 6.

- ▶ Bits 16 through 20 encoded with 0b00101 (5) for GPR 5.

- ▶ Bit 21 cleared (0) to disable overflow recording (using the mnemonic **addo** sets this bit).

- ▶ Bits 22 through 30 encoded with 0b100001010 (266) to represent the extended opcode.

- Recording the condition of the result in the CR is disabled, because bit 31 is cleared (0).

During the execution of this instruction, the contents of GPR 6 are added to the contents of GPR 5, and the result is placed into GPR 3.

The instruction mulwo. r7, r8, r6 has:

- ▶ Bits 0 through 5 encoded with the bit value of 0b011111 (31) as the primary opcode.

- ▶ Bits 6 through 10 encoded with 0b00111 (7) for GPR 7.

- ▶ Bits 11 through 15 encoded with 0b01000 (8) for GPR 6.

- Bits 16 through 20 encoded with 0b00110 (6) for GPR 5.

Because of the letter *o* in the mnemonic, bit 21 is set to one (1). If an overflow condition occurs, it is recorded in the fixed-point exception register (XER). Bits 22 through 30 have the encoding of 0b011101011 (235). Because of the period (.) after the mnemonic, bit 31 is set to record (whether the result of the operation is less than zero, greater than zero, or equal to zero) in field 0 (CR0) of the CR. During the execution of this instruction, the contents of GPR 8 is multiplied by the contents of GPR 6, and the result is placed into GPR 7. If an overflow occurs, the CR and XER are also updated.

PowerPC instructions are grouped into 28 functional categories from integer arithmetic instructions (add, subtract, multiply, and divide) to memory synchronization instructions (eieio, isync, and lwarz).

#### 1.6.1 Code example for a digital signal processing filter

The code examples in this section illustrate the use of PowerPC instructions. This example is for digital signal processing. Formulas using dot product notation represent the core of DSP algorithms. In fact, matrix multiplication forms the basis of much scientific programming. Example 1-1 shows the C source for the example of a matrix product.

Example 1-1 Matrix product: C source code

```

for ( i = 0; i < 10; i++ )

{

for ( j = 0; j < 10; j++ )

{

c[i][j] = 0;

for ( k = 0; k < 10; k++ )

{

c[i][j] = c[i][j] + a[i][k] * b[k][j];

}

}

}</pre>

```

The central fragment and inner loop code for Example 1-1 is:

```

c[i][j] = c[i][j] + a[i][k] * b[k][j];

```

This example assumes that:

- ► GPR A (rA) points to array a

- ► GPR B (rB) points to array b

- ▶ GPR C (rC) points to array c

Example 1-2 on page 17 shows the assembly code for the double-precision floating-point case. The multiply-add instructions and update forms of the load and store instructions combine to form a tight loop. This example represents an extremely naive compilation that neglects loop transformations.

Example 1-2 Assembly code

```

rA, rA, -8

# Back off addresses by 8 bytes for going into loop

addi

rB, rB, -8

addi rC, rC, -8

addi rD, 0, 10

# Put 10 into rD

mtspr 9, rD

# Place 10 into count register (SPR 9)

loop:

1fdu FRO, 8(rA)

# Load a[i][j], update rA to next element (rA=RA+8)

1fdu

FR1, 8(rB)

# Load b[k][j], update rB to next element (rB=rB+8)

fmadd FR2, FR0, FR1, FR2

# Multiply contents of FRO by FR1 then add FR2

bdnz loop

# Decrement count register and branch if not zero

stfdu FR2, 8(rC)

# Store c[i][j] element, update rC (rC=rC+8)

```

The reason we have to "back off" the addresses prior to going into the loop is because the  $1 \, fdu$  and stfdu instructions generate the effective address first by adding the displacement value (8) to the contents of the GPR. The result of this addition is placed back into the GPR (for example, rA = rA + 8). If not, the loop would skip over the first 8 bytes (64 bits) of the matrix. The fmadd instruction, first introduced in the POWER architecture, performs a multiply and add operation within one instruction. Because normalization and rounding occurs after the completion of both operations, the rounding error is effectively cut in half as compared to doing these as separate instructions (for example, multiply instruction followed by an add instruction).

#### 1.7 Superscalar and pipelining

To this point, the paper has described registers and instructions. One major feature of the PowerPC microprocessors is to execute instructions in parallel. Often the term *superscalar* appears in the description of an IBM @server system and are not quite sure what that term represents. For those readers who are actively or considering writing assembly language programs for the PowerPC 970, a brief description is presented here.

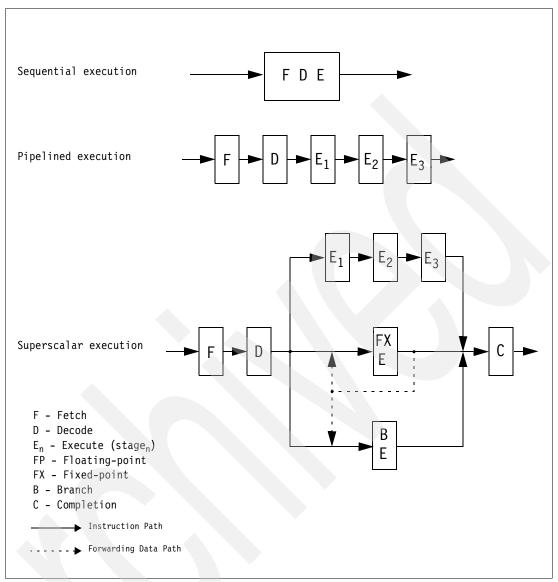

Figure 1-1 on page 8 showed the block diagram of the PowerPC 970 with its 10 pipelines (CR, BR, FP1, FP2, VPERM, VALU, FX1, FX2, LS1 and LS2) for instruction execution. The PowerPC architecture requires a sequential execution model in which each instruction appears to complete before the next instruction starts from the perspective of the programmer. Because only the appearance of sequential execution is required, implementations are free to process instructions using any technique so long as the programmer can observe only sequential execution. Figure 1-6 on page 23 shows a series of progressively more complex processor implementations.

Figure 1-6 Processor implementations

The sequential execution implementation fetches, decodes, and executes one instruction at a time in program order so that a program modifies the processor and memory state one instruction at a time in program order. This implementation represents the sequential execution model that a programmer expects.