# Performance Optimization and Tuning Techniques for IBM Power Systems Processors Including IBM POWER8

Peter Bergner

Bernard King Smith

Brian Hall

Julian Wang

Alon Shalev Housfater

Suresh Warrier

Madhusudanan Kandasamy

**David Wendt**

Tulio Magno

Alex Mericas

Steve Munroe

Mauricio Oliveira

Bill Schmidt

Will Schmidt

**Power Systems**

International Technical Support Organization

Performance Optimization and Tuning Techniques for IBM Power Systems Processors Including IBM POWER8

August 2015

| <b>Note:</b> Before using this information and the product it supports, read the information in "Notices" on page ix.                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                      |

| Second Edition (August 2015)                                                                                                                                                                                                                                         |

| This edition pertains to IBM Power Systems servers based on IBM Power Systems processor-based technology, including but not limited to IBM POWER8 processor-based systems. Specific software levels and firmware levels that are used are noted throughout the text. |

© Copyright International Business Machines Corporation 2014, 2015. All rights reserved.

Note to U.S. Government Users Restricted Rights -- Use, duplication or disclosure restricted by GSA ADP Schedule

Contract with IBM Corp.

# **Contents**

| NoticesixTrademarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBM Redbooks promotions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PrefacexiiAuthorsxiiNow you can become a published author, too!xviComments welcomexviStay connected to IBM Redbooksxvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Summary of changes xix August 2015, Second Edition xix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 1. Optimization and tuning on IBM POWER8 processor-based systems  1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 2. The IBM POWER8 processor252.1 Introduction to the POWER8 processor262.2 Using POWER8 features262.2.1 Multi-core and multi-thread262.2.2 Multipage size support (page sizes (4 KB, 64 KB, 16 MB, and 16 GB))322.2.3 Efficient use of cache and memory332.2.4 Transactional memory422.2.5 Vector Scalar eXtension442.2.6 Decimal floating point472.2.7 In-core cryptography and integrity enhancements472.2.8 On-chip accelerators482.2.9 Storage synchronization (sync, lwsync, lwarx, stwcx., and eieio)482.2.10 Fixed-point load and store quadword instructions562.2.11 Instruction fusion562.2.12 Event-based branches (or user-level fast interrupts)522.2.13 Power management and system performance522.2.14 Coherent Accelerator Processor Interface532.3 I/O adapter affinity582.4 Related publications58 |

| Chapter 3. The IBM POWER Hypervisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2.3 Placing LPAR resources to attain higher memory affinity                      |      |

|------------------------------------------------------------------------------------|------|

| 3.2.5 Optimizing resource placement: Dynamic Platform Optimizer                    |      |

| 3.2.6 Partition compatibility mode                                                 |      |

| 3.3 Introduction to KVM Virtualization                                             |      |

| 3.4 Related publications                                                           |      |

| C.+ Holatou publications                                                           | . 00 |

| Chapter 4. IBM AIX                                                                 | . 71 |

| 4.1 Introduction                                                                   | . 72 |

| 4.2 Using Power Architecture features with AIX                                     | . 72 |

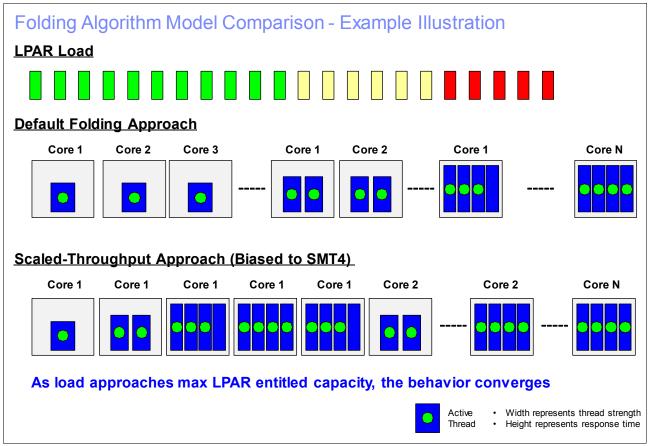

| 4.2.1 Multi-core and multi-thread                                                  | . 72 |

| 4.2.2 Multipage size support on AIX                                                | . 83 |

| 4.2.3 Efficient use of cache                                                       | . 86 |

| 4.2.4 Transactional memory                                                         | . 89 |

| 4.2.5 Vector Scalar eXtension                                                      | . 91 |

| 4.2.6 Decimal floating point                                                       | . 92 |

| 4.2.7 On-chip encryption accelerator                                               | . 94 |

| 4.3 AIX operating system-specific optimizations                                    | . 95 |

| 4.3.1 Malloc                                                                       | . 95 |

| 4.3.2 Pthread tunables                                                             | . 97 |

| 4.3.3 pollset                                                                      | . 98 |

| 4.3.4 File system performance benefits                                             | . 98 |

| 4.3.5 Direct I/O                                                                   | . 98 |

| 4.3.6 Concurrent I/O                                                               |      |

| 4.3.7 Asynchronous I/O                                                             |      |

| 4.3.8 I/O completion ports                                                         |      |

| 4.3.9 shmat versus mmap                                                            |      |

| 4.3.10 Large segment tunable aliasing (LSA)                                        |      |

| 4.3.11 64-bit versus 32-bit ABIs                                                   |      |

| 4.3.12 Sleep and wake-up primitives (thread_wait and thread_post)                  |      |

| 4.3.13 Shared versus private loads                                                 |      |

| 4.3.14 Workload partition shared licensed program installations                    |      |

| 4.4 AIX preferred practices                                                        |      |

| 4.4.1 AIX preferred practices that are applicable to all Power Systems generations | 105  |

| 4.4.2 AIX preferred practices that are applicable to POWER7 and POWER8             |      |

| processor-based systems                                                            |      |

| 4.5 Related publications                                                           | 107  |

| Chanter 5 IDM:                                                                     | 444  |

| Chapter 5. IBM i                                                                   |      |

| 5.2 Using Power features with IBM i                                                |      |

| 5.2.1 Multi-core and multi-thread                                                  |      |

| 5.2.2 Multipage size support on IBM i                                              |      |

| 5.2.3 Vector Scalar eXtension                                                      |      |

| 5.2.4 Decimal floating point                                                       |      |

| 5.3 IBM i operating system-specific optimizations.                                 |      |

| 5.3.1 IBM i advanced optimization techniques                                       |      |

| 5.3.2 Performance management on IBM i                                              |      |

| 5.4 Related publications                                                           |      |

| o. Holatoa pabiloationo                                                            |      |

| Chapter 6. Linux                                                                   | 117  |

| 6.1 Introduction                                                                   |      |

| 6.2 Using Power features with Linux                                                | 118  |

| 6.2.1 Multi-core and multi-thread                                                  | 119  |

| 6.2.2 Multipage size support on Linux16.2.3 Efficient use of cache16.2.4 Transactional memory16.2.5 Vector Scalar eXtension16.2.6 Decimal floating point16.2.7 Event-based branches16.3 Linux operating system-specific optimizations16.3.1 GCC, toolchain, and IBM Advance Toolchain16.3.2 Tuning and optimizing malloc16.3.3 Large TOC -mcmodel=medium optimization16.3.4 POWER7 based distro considerations16.3.5 Microthreading considerations16.4 Little Endian16.4.1 Application binary interface16.5 Related publications1 | 123<br>124<br>125<br>126<br>128<br>129<br>133<br>137<br>137<br>137<br>138 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Chapter 7. Compilers and optimization tools for C, C++, and Fortran                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 141                                                                       |

| 7.1 Compiler versions and optimization levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

| 7.2 Advanced compiler optimization techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

| 7.2.1 Common prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

| 7.2.2 XL compiler family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| 7.2.3 GCC compiler family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 146                                                                       |

| 7.3 Capitalizing on POWER8 features with the XL and GCC compilers 1                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 148                                                                       |

| 7.3.1 In-core cryptography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 148                                                                       |

| 7.3.2 Compiler support for Vector Scalar eXtension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| 7.3.3 Built-in functions for storage synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

| 7.3.4 Data Streams Control Register controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

| 7.3.5 Transactional memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

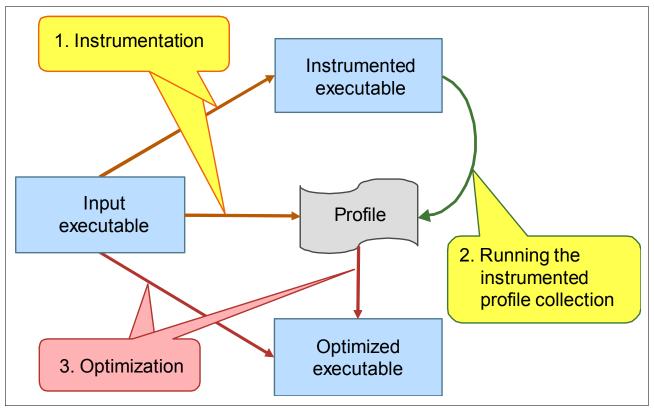

| 7.4 IBM Feedback Directed Program Restructuring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| 7.4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| 7.4.2 Feedback Directed Program Restructuring supported environments                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

| 7.4.3 Acceptable input formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

| 7.4.4 General operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

| 7.4.5 Instrumentation and profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

| 7.4.6 Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| 7.6 Using GPU accelerators with C/C++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 171                                                                       |

| 7.7 Neiateu publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 171                                                                       |

| Chapter 8. Java                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 173                                                                       |

| 8.1 Java levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174                                                                       |

| 8.2 32-bit versus 64-bit Java 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 174                                                                       |

| 8.2.1 Little Endian support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 175                                                                       |

| 8.3 Memory and page size considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 175                                                                       |

| 8.3.1 Medium and large pages for Java heap and code cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 175                                                                       |

| 8.3.2 Configuring large pages for Java heap and code cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

| 8.3.3 Prefetching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 177                                                                       |

| 8.3.5 JIT code cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

| 8.3.6 Shared classes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

| 8.4 Capitalizing on POWER8 features with IBM Java                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

| 8.4.1 In-core Advanced Encryption Standard and Secure Hash Algorithm acceleration a                                                                                                                                                                                                                                                                                                                                                                                                                                               | ınd                                                                       |

| 8.4.2 Transactional memory                                                          |       |

|-------------------------------------------------------------------------------------|-------|

| 8.4.3 Runtime instrumentation                                                       | . 183 |

| 8.5 Java garbage collection tuning                                                  |       |

| 8.5.1 GC strategy: Optthruput                                                       |       |

| 8.5.2 GC strategy: Optavgpause                                                      | 184   |

| 8.5.3 GC strategy: Gencon                                                           | . 184 |

| 8.5.4 GC strategy: Balanced                                                         | 184   |

| 8.5.5 Optimal heap size                                                             | . 185 |

| 8.6 Application scaling                                                             | 186   |

| 8.6.1 Choosing the correct simultaneous multithreading mode                         | 186   |

| 8.6.2 Using resource sets                                                           | . 187 |

| 8.6.3 Java lock reservation                                                         | 189   |

| 8.6.4 Java GC threads                                                               | . 189 |

| 8.6.5 Java concurrent marking                                                       | . 189 |

| 8.7 Using GPU accelerators with IBM Java                                            | 190   |

| 8.7.1 Automatic GPU compilation                                                     | 190   |

| 8.7.2 Accessing the GPU through the CUDA4J application programming interface        | . 191 |

| 8.7.3 The com.ibm.gpu application programming interface                             | . 191 |

| 8.7.4 NVIDIA Compute Unified Device Architecture: Java Native interface             |       |

| 8.8 Related publications                                                            | . 192 |

| ·                                                                                   |       |

| Chapter 9. IBM DB2                                                                  |       |

| 9.1 DB2 and the POWER processor                                                     |       |

| 9.2 Taking advantage of the POWER processor                                         |       |

| 9.2.1 Affinitization                                                                |       |

| 9.2.2 Page sizes                                                                    |       |

| 9.2.3 Decimal arithmetic                                                            |       |

| 9.2.4 Using simultaneous multithreading priorities for internal lock implementation |       |

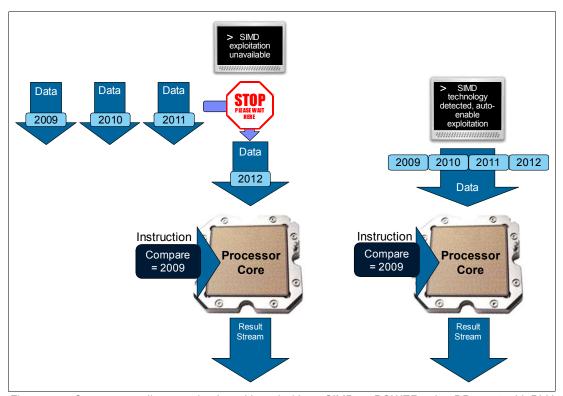

| 9.2.5 Single Instruction Multiple Data                                              |       |

| 9.3 Capitalizing on the compilers and optimization tools for POWER                  |       |

| 9.3.1 Whole-program analysis and profile-based optimizations                        |       |

| 9.3.2 IBM Feedback Directed Program Restructuring                                   |       |

| 9.4 Capitalizing on POWER virtualization                                            | . 198 |

| 9.4.1 DB2 virtualization                                                            |       |

| 9.4.2 DB2 in an AIX workload partition                                              | . 199 |

| 9.5 Capitalizing on the AIX system libraries                                        | . 199 |

| 9.5.1 Using the thread_post_many API                                                | . 199 |

| 9.5.2 File systems                                                                  |       |

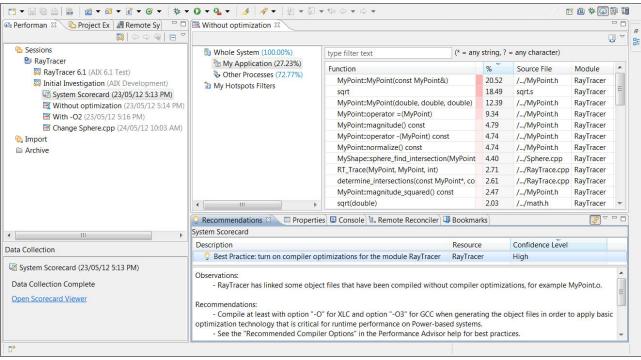

| 9.6 Capitalizing on performance tools                                               | 201   |

| 9.6.1 High-level investigation                                                      | 201   |

| 9.6.2 Low-level investigation                                                       | 201   |

| 9.7 Conclusion                                                                      | 202   |

| 9.8 Related publications                                                            | 202   |

|                                                                                     |       |

| Chapter 10. IBM WebSphere Application Server                                        |       |

| 10.1 IBM WebSphere                                                                  |       |

| 10.1.1 Installation                                                                 |       |

| 10.1.2 Deployment                                                                   |       |

| 10.1.3 Performance                                                                  |       |

| 10.1.4 Performance analysis, problem determination, and diagnostic tests            | 209   |

| Appendix A. Analyzing malloc usage under IBM AIX                                    | 211   |

| Introduction                                                                        |       |

| How to collect malloc usage information                                             |       |

| TION to concet mande adage information                                              | -12   |

| Appendix B. Performance tools and empirical performance analysis                   |     |

|------------------------------------------------------------------------------------|-----|

| Performance advisors                                                               |     |

| Expert system advisors                                                             |     |

| · · ·                                                                              |     |

| IBM Rational Performance Advisor                                                   |     |

| IBM Power Virtualization Performance                                               |     |

| AIX                                                                                |     |

| CPU profiling                                                                      |     |

| AIX trace-based analysis tools                                                     | 226 |

| Finding emulation issues                                                           | 232 |

| hpmstat, hpmcount, and tprof -E                                                    | 232 |

| Linux                                                                              |     |

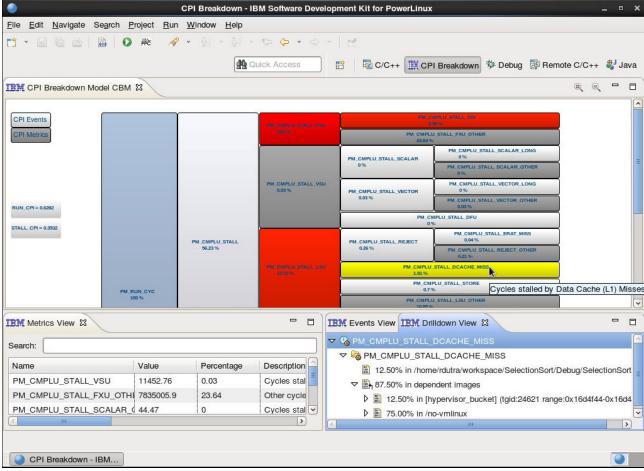

| Empirical performance analysis by using the IBM Software Development Kit for Linux |     |

| Power                                                                              |     |

| Using the IBM SDK for Linux on Power Trace Analyzer                                |     |

| High library usage                                                                 |     |

| Deeper empirical analysis                                                          |     |

| · · · · · · · · · · · · · · · · · · ·                                              |     |

| Java (either AIX or Linux)                                                         |     |

| 32-bit or 64-bit JDK                                                               |     |

| Java heap size, and garbage collection policies and parameters                     |     |

| Hot method or routine analysis                                                     | 241 |

| Locking analysis                                                                   | 246 |

| Thread state analysis                                                              | 246 |

# **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not grant you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive, Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM websites are provided for convenience only and do not in any manner serve as an endorsement of those websites. The materials at those websites are not part of the materials for this IBM product and use of those websites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Any performance data contained herein was determined in a controlled environment. Therefore, the results obtained in other operating environments may vary significantly. Some measurements may have been made on development-level systems and there is no guarantee that these measurements will be the same on generally available systems. Furthermore, some measurements may have been estimated through extrapolation. Actual results may vary. Users of this document should verify the applicable data for their specific environment.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrate programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs.

### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation in the United States, other countries, or both. These and other IBM trademarked terms are marked on their first occurrence in this information with the appropriate symbol (® or ™), indicating US registered or common law trademarks owned by IBM at the time this information was published. Such trademarks may also be registered or common law trademarks in other countries. A current list of IBM trademarks is available on the Web at http://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

Active Memory™ Power Architecture® PowerPC® **AIX®** POWER Hypervisor™ PowerVM® AIX 5L™ Power Systems™ PowerVP™ Blue Gene/L® Power Systems Software™ Rational® DB2® POWER6® Redbooks® **FDPR®** POWER6+™ Redbooks (logo) @® **IBM®** POWER7® System z® IBM Watson™ Tivoli® POWER7+™ Micro-Partitioning® POWER8® WebSphere®

POWER® PowerLinux™

The following terms are trademarks of other companies:

Intel, Intel logo, Intel Inside logo, and Intel Centrino logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

LTO, the LTO Logo and the Ultrium logo are trademarks of HP, IBM Corp. and Quantum in the U.S. and other countries.

Windows, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java, and all Java-based trademarks and logos are trademarks or registered trademarks of Oracle and/or its affiliates.

UNIX is a registered trademark of The Open Group in the United States and other countries.

Other company, product, or service names may be trademarks or service marks of others.

# Find and read thousands of **IBM Redbooks publications**

- ► Search, bookmark, save and organize favorites

- ► Get up-to-the-minute Redbooks news and announcements

- Link to the latest Redbooks blogs and videos

Get the latest version of the Redbooks Mobile App

# **Promote your business** in an IBM Redbooks publication

Place a Sponsorship Promotion in an IBM® Redbooks® publication, featuring your business or solution with a link to your web site.

Qualified IBM Business Partners may place a full page promotion in the most popular Redbooks publications. Imagine the power of being seen by users who download millions of Redbooks publications each year!

ibm.com/Redbooks About Redbooks → Business Partner Programs

# **Preface**

This IBM® Redbooks® publication focuses on gathering the correct technical information, and laying out simple guidance for optimizing code performance on IBM POWER8® processor-based systems that run the IBM AIX®, IBM i, or Linux operating systems. There is straightforward performance optimization that can be performed with a minimum of effort and without extensive previous experience or in-depth knowledge.

The POWER8 processor contains many new and important performance features, such as support for eight hardware threads in each core and support for transactional memory. The POWER8 processor is a strict superset of the IBM POWER7+™ processor, and so all of the performance features of the POWER7+ processor, such as multiple page sizes, also appear in the POWER8 processor. Much of the technical information and guidance for optimizing performance on POWER8 processors that is presented in this guide also applies to POWER7+ and earlier processors, except where the guide explicitly indicates that a feature is new in the POWER8 processor.

This guide strives to focus on optimizations that tend to be positive across a broad set of IBM POWER® processor chips and systems. Specific guidance is given for the POWER8 processor; however, the general guidance is applicable to the IBM POWER7+, IBM POWER6®, IBM POWER5, and even to earlier processors.

This guide is directed at personnel who are responsible for performing migration and implementation activities on POWER8 processor-based systems. This includes system administrators, system architects, network administrators, information architects, and database administrators (DBAs).

# **Authors**

This book was produced by a team of specialists from around the world working at the International Technical Support Organization, Poughkeepsie Center.

Peter Bergner is the GCC Compiler Team Lead within the Linux on Power Toolchain department. Since joining IBM in 1996, Peter has worked in various areas, including compiler optimizer development for the IBM i platform, as a core member of the teams that ported Linux and GLIBC to 64-bit POWER, and as a team lead for the IBM Blue Gene/L® compiler and runtime library development team. He obtained a PhD in Electrical Engineering from the University of Minnesota.

**Brian Hall** is the lead analyst for performance improvement efforts with the IBM Cloud Innovation Laboratory team. He works with many IBM software products to capitalize on the IBM Power Architecture® and develop performance preferred practices for software development and deployment. After joining IBM in 1987, Brian originally worked on the IBM XL C/C++/Fortran compilers and on the just-in-time compiler for IBM Java on Power. He has a Bachelor's degree in Computer Science from Queen's University at Kingston and a Master's degree in Computer Science from the University of Toronto.

**Alon Shalev Housfater** is software engineering professional at the IBM Runtime Technology Center at the IBM Toronto Lab. Alon's role involves deep system performance analysis and the exploitation of computational accelerators by Java's Just-in-Time compiler. He holds a PhD degree in Electrical Engineering from the University of Toronto.

**Madhusudanan Kandasamy** is an IBM Master Inventor and Technical Chief Engineering Manager (TCEM) for AIX Performance, Scalability, and DSO. He has more than a decade of experience in AIX development. He holds a Master's degree in Software Systems from Birla Institute of Technology, Pilani-India.

**Tulio Magno** is a Staff Software Engineer at the Linux Technology Center. He holds a Bachelor's degree in Electrical Engineering from Federal University of Minas Gerais and has been working on the Linux Toolchain for the last four years developing core libraries and the Advanced Toolchain.

**Alex Mericas** is a member of the IBM Systems and Technology Group in Austin, Texas. He is a Senior Technical Staff Member and is the Performance Architect for the POWER8 processor. He designed the performance monitoring unit on POWER4, POWER5, POWER6, POWER7, and IBM PowerPC® 970 processor-based systems. Alex is an IBM Master Inventor with 47 US patent applications and 22 issued patents covering microprocessor design and hardware performance monitors.

Steve Munroe is a Senior Technical Staff Member at the Rochester, Minnesota Lab in IBM US. He has 38 years of experience in the software development field. He holds a Bachelor's degree in Computer Science from Washington State University (1974). His areas of expertise include PowerISA, compilers, POSIX run times, and performance analysis. He has written extensively about IBM POWER performance and Java performance.

Mauricio Oliveira is a Staff Software Engineer at the Linux Technology Center at IBM Brazil. His areas of expertise include Linux performance and Debian and Ubuntu distributions on IBM Power Systems<sup>™</sup>. He also worked with official benchmark publications for Linux on IBM Power Systems and early development (bootstrap) of Debian on Little Endian 64-bit PowerPC. Mauricio holds a Master of Computer Science and Technology degree and a Bachelor of Engineering degree in Computer Engineering from Federal University of Itajubá, Brazil.

**Bill Schmidt** is a Senior Software Engineer with IBM in Rochester, Minnesota. He has 22 years of experience with design and implementation of compilers for the Power architecture, specializing in optimization technology. He contributes to the GCC and LLVM open source compilers. Bill is an IBM Master Inventor with over 50 issued US patents, and holds a PhD from Iowa State University.

Will Schmidt is an Advisory Software Engineer in Rochester, Minnesota. Since joining IBM in 1997, he has worked in various areas, most recently including Linux Toolchain and performance tools development. He obtained a BS in Mathematics and a BS in Computer Science from Bemidji State University.

Bernard King Smith is a Senior Software Engineer in the Power Systems Performance Department. He joined IBM in 1989 and has spent over 28 years in network performance of High Performance Computing (HPC) and clustered commercial systems. His primary work has been in TCP/IP and RDMA performance of high-speed networks. He was involved in the tuning and design of internal networks for both the IBM Deep Blue Chess Machine and the Jeopardy! Watson System. He is also the leading performance expert of InfiniBand network performance on Power Systems. He is an author or co-author of two patents and one Internet Engineering Task Force (IETF) standard. He is the team lead for networking performance for IBM Power Systems.

**Julian Wang** is the technical lead of JIT compiler and Java performance on Power Systems, and has been developing compiler and runtime products for the past 20 years. He has a passion for making the POWER architecture perform Java better and acute interests in parallel computing, operating system, performance analysis, and bit-twiddling.

Suresh Warrier is a Senior Technical Staff Member in IBM Power Systems Software™, specializing in KVM and Linux on Power architecture. Suresh has over 25 years of experience in systems software, including over 15 years leading AIX exploitation of POWER hardware technology. He has a Bachelor's degree in Electrical Engineering from the Indian Institute of Technology, Madras, India, and a Master's Degree in Computer Science from the University of Texas, Austin.

**David Wendt** is a Senior Staff Member of the IBM Watson<sup>™</sup> Performance team in Research Triangle Park, NC. He has a Master's degree in Electrical Engineering from Johns Hopkins University. He is also an IBM Master Inventor with 12 granted US patents in software development.

Thanks to the following people for their contributions to this project:

- ► For technical reviews:

- Clark Anderson, IBM Power Systems Storage I/O Subsystem Performance, Rochester, Minnesota

- Yaoqing Gao, Senior Technical Staff Member, XL C/C++ and Fortran compilers, Ontario, Canada

- Jenifer Hopper, Software Engineer Linux Performance Analyst, Austin, Texas

- Yan Luo, JIT Compiler POWER Optimization, Ontario, Canada

- Younes Manton, JIT Compiler POWER Optimization, Ontario, Canada

- Bruce Mealy, AIX Kernel Development, Austin, Texas

- Greg Mewhinney, Power Systems Performance, Austin, Texas

- Steve Munroe, Linux Toolchain Architect and TCEM, Rochester, Minnesota

- David Tam, Ph.D., Staff Software Developer, Ontario, Canada

- ► For overall contributions to this project:

- International Technical Support Organization, Poughkeepsie Center

- Deana Coble, IBM Redbooks Technical Writer, RTP, North Carolina

Thanks to the authors of the previous versions of this book:

Ryan Arnold, Peter Bergner, Wainer dos Santos Moschetta, Robert Enenkel, Pat Haugen, Michael R. Meissner, Alex Mericas, Bernie Schiefer, Suresh Warrier, Daniel Zabawa, Adhemerval Zanella

Brian Hall, Mala Anand, Bill Buros, Miso Cilimdzic, Hong Hua, Judy Liu, John MacMillan, Sudhir Maddali, K Madhusudanan, Bruce Mealey, Steve Munroe, Francis P O'Connell, Sergio Reyes, Raul Silvera, Randy Swanberg, Brian Twichell, Brian F Veale, Julian Wang, Yaakov Yaari

# Now you can become a published author, too!

Here's an opportunity to spotlight your skills, grow your career, and become a published author—all at the same time! Join an ITSO residency project and help write a book in your area of expertise, while honing your experience using leading-edge technologies. Your efforts will help to increase product acceptance and customer satisfaction, as you expand your network of technical contacts and relationships. Residencies run from two to six weeks in length, and you can participate either in person or as a remote resident working from your home base.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

## Comments welcome

Your comments are important to us!

We want our books to be as helpful as possible. Send us your comments about this book or other IBM Redbooks publications in one of the following ways:

▶ Use the online **Contact us** review Redbooks form found at:

ibm.com/redbooks

Send your comments in an email to:

redbooks@us.ibm.com

► Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. HYTD Mail Station P099 2455 South Road Poughkeepsie, NY 12601-5400

# Stay connected to IBM Redbooks

► Find us on Facebook:

http://www.facebook.com/IBMRedbooks

► Follow us on Twitter:

http://twitter.com/ibmredbooks

► Look for us on LinkedIn:

http://www.linkedin.com/groups?home=&gid=2130806

► Explore new Redbooks publications, residencies, and workshops with the IBM Redbooks weekly newsletter:

https://www.redbooks.ibm.com/Redbooks.nsf/subscribe?OpenForm

► Stay current on recent Redbooks publications with RSS Feeds:

http://www.redbooks.ibm.com/rss.html

# **Summary of changes**

This section describes the technical changes that are made in this edition of the book and in previous editions. This edition might also include minor corrections and editorial changes that are not identified.

Summary of Changes for SG24-8171-01 for Performance Optimization and Tuning Techniques for IBM Power Systems Processors Including IBM POWER8 as created or updated on March 31, 2017.

# **August 2015, Second Edition**

The second edition of this guide contains numerous minor updates and extensions across many topics, plus coverage of some new topics. Many of the updates are concentrated in Chapter 6, "Linux" on page 117, and are related to new developments in Linux for the POWER8 processor, such as Ubuntu for Power. Chapter 8, "Java" on page 173 contains updates covering the release of Java 8.

Coverage has been added for the following new topics:

- ► SMT modes as a deployment option (see "SMT mode" on page 19)

- ▶ Power management modes as a deployment option (see "Power management mode" on page 21)

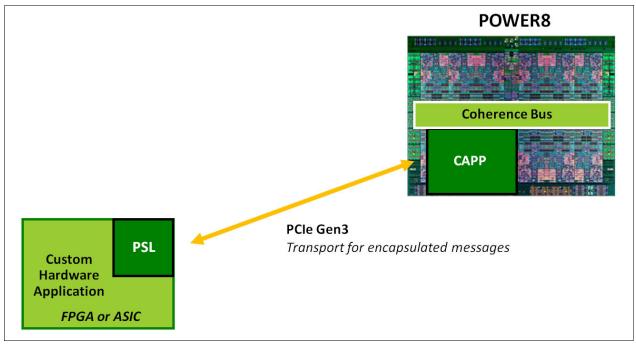

- ► Coherent Accelerator Processor Interface (CAPI) (see 2.2.14, "Coherent Accelerator Processor Interface" on page 53)

- ▶ I/O adapter affinity performance considerations (see 2.3, "I/O adapter affinity" on page 55)

- ► PowerKVM (see 3.3, "Introduction to KVM Virtualization" on page 67)

- ► Little Endian (see 6.4, "Little Endian" on page 138)

- ► GPU acceleration for C/C++ (7.6, "Using GPU accelerators with C/C++" on page 169)

- ► GPU acceleration for Java (8.7, "Using GPU accelerators with IBM Java" on page 190)

# 1

# Optimization and tuning on IBM POWER8 processor-based systems

This chapter describes the optimization and tuning of IBM POWER8 processor-based systems. It covers the following topics:

- ► 1.1, "Introduction" on page 2

- ▶ 1.2, "Outline of this guide" on page 2

- 1.3, "Conventions that are used in this guide" on page 5

- 1.4, "Background" on page 5

- ▶ 1.5, "Optimizing performance on POWER8 processor-based systems" on page 6

### 1.1 Introduction

This guide gathers the correct technical information and lays out simple guidance for optimizing code performance on IBM Power Systems that run the AIX, IBM i, or Linux operating systems.

This guide focuses on optimizations that tend to be positive across a broad set of IBM POWER processor chips and systems. Much of the technical information and guidance for optimizing performance on the POWER8 processor that is presented in this guide also applies to POWER7+ and earlier processors, except where the guide explicitly indicates that a feature is new in the POWER8 processor.

Straightforward performance optimization can be performed with a minimum of effort and without extensive previous experience or in-depth knowledge. This optimization work can accomplish the following goals:

- ► Substantially improve the performance of the application that is being optimized for the POWER8 processor (the focus of this guide).

- ► Typically, carry over improvements to systems that are based on related processor chips, such as the IBM POWER7+, IBM POWER7, and IBM POWER6 processor chips.

- ► Improve performance on other platforms.

The POWER8 processor contains many new and important performance features, such as support for eight hardware threads in each core and support for transactional memory. The POWER8 processor is a strict superset of the POWER7+ processor, and so all of the performance features of the POWER7+ processor, such as multiple page sizes, also appear in the POWER8 processor.

This guide is directed at personnel who are responsible for performing migration and implementation activities on POWER8 processor-based systems, including systems administrators, system architects, network administrators, information architects, program product developers, software architects, database administrators (DBAs), and compiler writers.

# 1.2 Outline of this guide

This chapter lays out simple strategies for optimizing performance and covers the opportunities that have been found to be the most universally applicable and valuable in past performance efforts (see 1.5, "Optimizing performance on POWER8 processor-based systems" on page 6). This chapter is not an exhaustive guide to Power Systems performance, but it presents a concise overview of typical methodology and areas to focus on in a performance improvement effort. There are references to later chapters in the guide that present a complete technical description of these areas. Later chapters also contain a complete list of opportunities and techniques to optimize performance that might be valuable in particular cases.

Section 1.5.1, "Lightweight tuning and optimization guidelines" on page 7 describes a set of straightforward steps to set up the environment for performance tuning and optimization, followed by an explanation about how to perform a set of straightforward and easy investigative steps. These steps are the most valuable to focus on for a short performance effort. These steps do not require a deep level of knowledge of the application being optimized, and (with one minor exception) do not involve changing application source code.

Section 1.5.2, "Deployment guidelines" on page 15 describes deployment choices, that is, system setup and configuration choices, so you can tune these designed-for-performance IBM Power Systems for your environment. Together with 1.5.1, "Lightweight tuning and optimization guidelines" on page 7, these simple optimization strategies and deployment guidance satisfy the requirements for most environments and can deliver substantial improvements.

Finally, 1.5.3, "Deep performance optimization guidelines" on page 21 describes some of the more advanced investigative techniques that can be used to identify performance bottlenecks in an application. It is here that optimization efforts move into the application code, and improvements are typically made by modifying source code. Coverage in this last area is fairly rudimentary, focusing on general areas of investigation and the tools that you can use.

Most of the remaining material in this guide is technical information that was developed by domain experts at IBM:

- ► This guide provides hardware information about the POWER8 processor (see Chapter 2, "The IBM POWER8 processor" on page 25), highlighting the important features from a performance perspective and laying out the basic information that is drawn upon by the material that follows.

- ► This guide describes the system software stack, examining the IBM POWER Hypervisor<sup>TM</sup> (see Chapter 3, "The IBM POWER Hypervisor" on page 57), the AIX, IBM i, and Linux operating systems and system libraries (see Chapter 4, "IBM AIX" on page 71, Chapter 5, "IBM i" on page 111, and Chapter 6, "Linux" on page 117), and the compilers (see Chapter 7, "Compilers and optimization tools for C, C++, and Fortran" on page 141). Java (see Chapter 8, "Java" on page 173) also receives extensive coverage.

- ► Chapter 4, "IBM AIX" on page 71 highlights some of the areas in which AIX exposes some new features of the POWER8 processor. Then, this chapter examines a set of operating system-specific optimization opportunities. The chapter concludes with a short description of AIX preferred practices regarding system setup and maintenance.

- ► Chapter 5, "IBM i" on page 111 describes IBM i support for a number of features in POWER8 processors (including features that are available in previous generations of POWER processors). The chapter describes how this operating system can be effective in automatically capitalizing on many new POWER architecture features without changes to existing programs. The chapter also provides information about IBM Portable Application Solutions Environment for i (PASE for i), a part of IBM i that allows some AIX application binary files to run on IBM i with little or no changes.

- ► Chapter 6, "Linux" on page 117 describes the primary Linux operating systems that are used on POWER8 processor-based systems. The chapter covers using features of the POWER architecture, and operating system-specific optimization opportunities.

- Linux is based on community efforts that are focused not only on the Linux kernel, but also all of the complementary packages, tools, toolchains, and GNU Compiler Collection (GCC) compilers that are needed to use effectively POWER8 processor-based systems. IBM provides the expertise for Power Systems by developing, optimizing, and pushing open source changes to the Linux communities.

- ► Chapter 7, "Compilers and optimization tools for C, C++, and Fortran" on page 141 describes current compiler versions and optimization levels and how, for projects with increased focus on runtime performance, you can take advantage of the more advanced compiler optimization techniques. It describes XL compiler static analysis and runtime checking to validate the correctness of the program.

- ► Chapter 8, "Java" on page 173 describes the optimization and tuning of Java based applications that are running in a POWER environment.

► Finally, this book covers important information about IBM middleware, DB2® (see Chapter 9, "IBM DB2" on page 193) and IBM WebSphere® Application Server (see Chapter 10, "IBM WebSphere Application Server" on page 205). Various applications use middleware, and it is critical that the middleware is tuned correctly and performs well. The middleware chapters cover how these products are optimized for POWER8 processor-based systems, including select preferred practices for tuning and deploying these products.

The following appendixes are included:

- ▶ Appendix A, "Analyzing malloc usage under IBM AIX" on page 211 explains some simple techniques for analyzing how an application is using the system memory allocation routines (*malloc* and related functions in the C library). malloc is often a bottleneck for application performance, especially under AIX. AIX has an extensive set of optimized malloc implementations, and it is easy to switch between them without rebuilding or changing an application. Knowing how an application uses malloc is key to choosing the best memory allocation alternatives that AIX offers. Even Java applications often make extensive use of malloc, either in Java Native Interface (JNI) code that is part of the application itself or in the Java class libraries, or in binary code that is part of the software development kit (SDK).

- ► Appendix B, "Performance tools and empirical performance analysis" on page 215 describes some of the important performance tools that are available on the IBM Power Architecture under AIX or Linux, and strategies for using them in empirical performance analysis efforts.

These performance tools are most often used as part of the advanced investigative techniques that are described in 1.5.3, "Deep performance optimization guidelines" on page 21, except for the performance advisors, which are intended as investigative tools that are appropriate for a broader audience of users.

Throughout the book, there are links to related sections among the chapters. For example, Vector Scalar eXtension (VSX) is described in the processor chapter (Chapter 2, "The IBM POWER8 processor" on page 25), all of the OS chapters (Chapter 4, "IBM AIX" on page 71, Chapter 5, "IBM i" on page 111, and Chapter 6, "Linux" on page 117), and in the compiler chapter (Chapter 7, "Compilers and optimization tools for C, C++, and Fortran" on page 141). Therefore, after the description of VSX in the processor chapter, there are links to that same section in the OS chapters and in the compiler chapter.

After you review the advice in this guide, for more information, visit the IBM Power Systems website at: