# IBM zEnterprise 196 Technical Guide

Redbooks

# International Technical Support Organization

# **IBM zEnterprise 196 Technical Guide**

October 2011

| <b>Note:</b> Before using this information and the product it supports, read the information in "Notices" on page xiii.             |

|-------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

|                                                                                                                                     |

| Second Edition (October 2011)                                                                                                       |

| Second Edition (October 2011)  This edition applies to the IBM zEnterprise 196 System. The changes to this edition are based on the |

| System z hardware announcement dated July 12, 2011.                                                                                 |

|                                                                                                                                     |

# **Contents**

| Notices                                                                  |     |

|--------------------------------------------------------------------------|-----|

| Trademarks                                                               | xiv |

| Preface                                                                  | χV  |

| The team who wrote this book                                             |     |

| Now you can become a published author, too!                              |     |

|                                                                          |     |

| Comments welcome.                                                        |     |

| Stay connected to IBM Redbooks publications                              | XIX |

| Chapter 1. Introducing the IBM zEnterprise 196                           | 1   |

| 1.1 zEnterprise 196 elements                                             |     |

| 1.2 zEnterprise 196 highlights                                           | 3   |

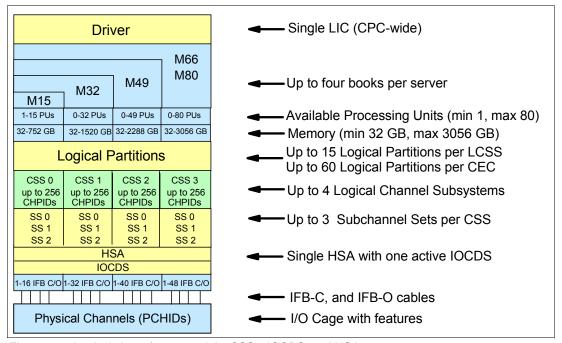

| 1.2.1 Models                                                             |     |

| 1.2.2 Capacity on Demand (CoD)                                           |     |

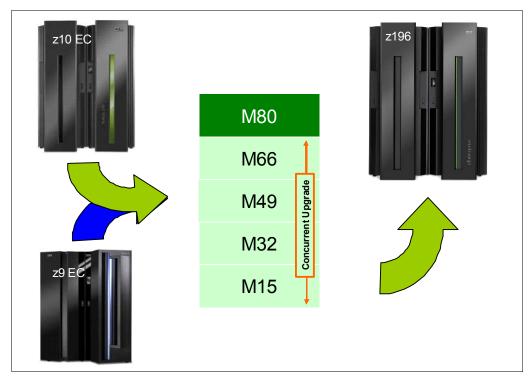

| 1.3 zEnterprise 196 models                                               |     |

| 1.3.1 Model upgrade paths                                                |     |

| 1.3.2 Concurrent processor unit conversions.                             |     |

| ·                                                                        |     |

| 1.4 System functions and features                                        |     |

| 1.4.1 Overview                                                           |     |

| 1.4.2 Processor                                                          |     |

| 1.4.3 Memory subsystem and topology                                      |     |

| 1.4.4 Processor cage                                                     |     |

| 1.4.5 I/O connectivity, PCIe, and InfiniBand                             |     |

| 1.4.6 I/O subsystems                                                     |     |

| 1.4.7 Cryptography                                                       |     |

| 1.4.8 Parallel Sysplex support                                           |     |

| 1.5 IBM zEnterprise BladeCenter Extension (zBX)                          | 15  |

| 1.5.1 Blades                                                             | 16  |

| 1.5.2 IBM Smart Analytics Optimizer solution                             | 16  |

| 1.5.3 IBM WebSphere DataPower Integration Appliance XI50 for zEnterprise | 17  |

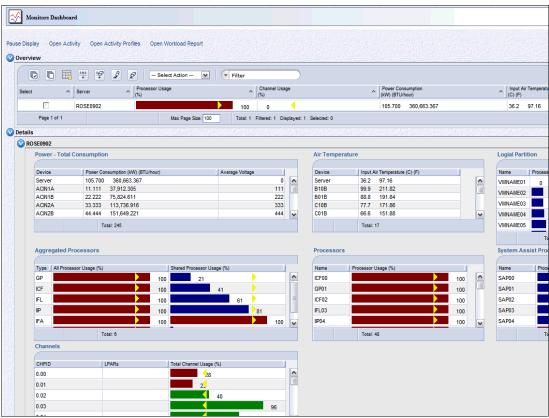

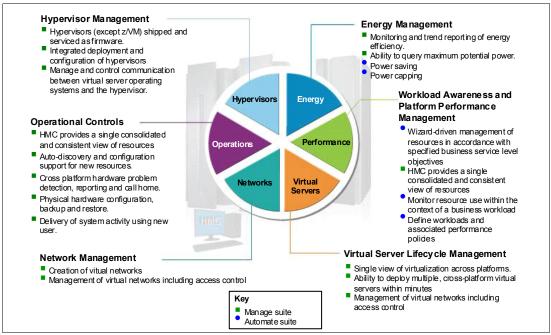

| 1.6 Unified Resource Manager                                             |     |

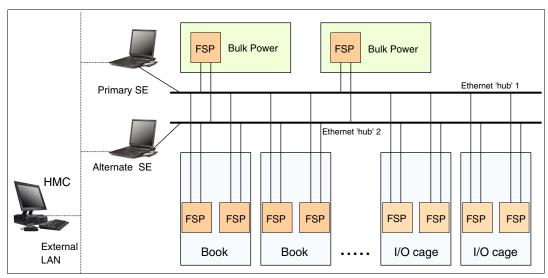

| 1.7 Hardware Management Consoles and Support Elements                    |     |

| 1.8 Reliability, availability, and serviceability                        |     |

| 1.9 Performance                                                          |     |

| 1.9.1 LSPR workload suite                                                |     |

| 1.9.2 Fundamental components of workload capacity performance            |     |

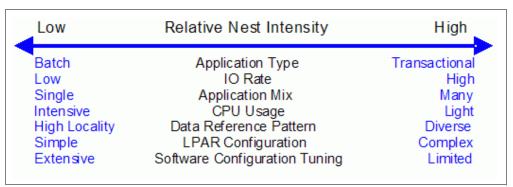

| 1.9.3 Relative nest intensity                                            |     |

| 1.9.4 LSPR workload categories based on relative nest intensity          |     |

|                                                                          |     |

| 1.9.5 Relating production workloads to LSPR workloads                    |     |

| 1.9.6 Workload performance variation                                     |     |

| 1.10 Operating systems and software                                      | 25  |

| Chapter 2. CPC hardware components                                       | 27  |

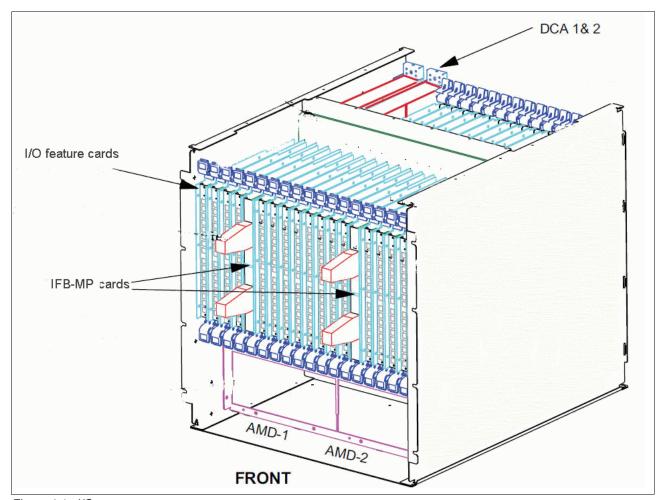

| 2.1 Frames and cage                                                      |     |

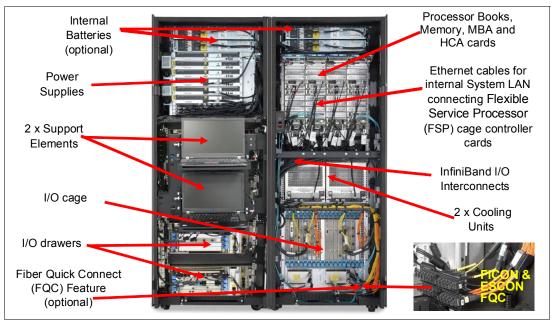

| 2.1.1 Frame A                                                            |     |

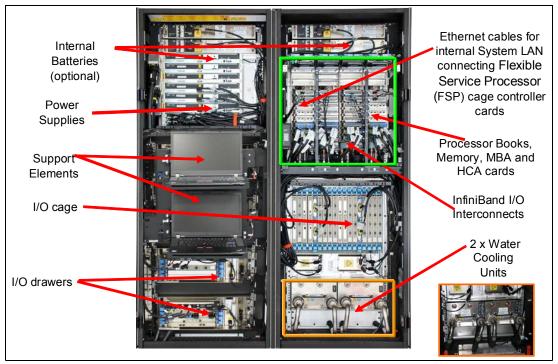

| 2.1.2 Frame Z                                                            |     |

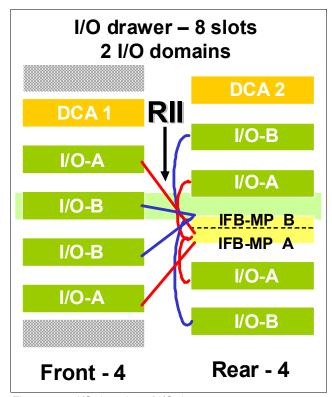

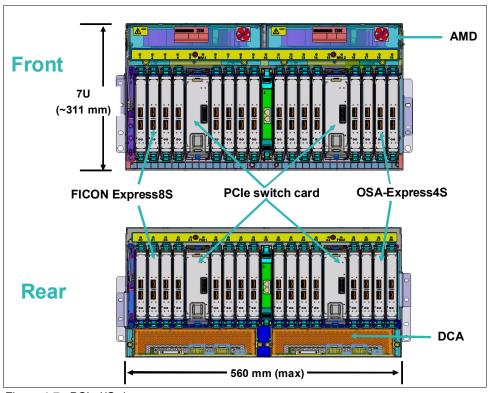

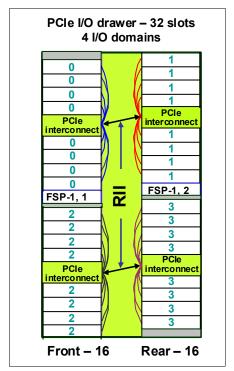

| 2.1.3 I/O cages, I/O drawers, and PCIe I/O drawers                       |     |

| 2.1.4 Top exit I/O cabling                                               |     |

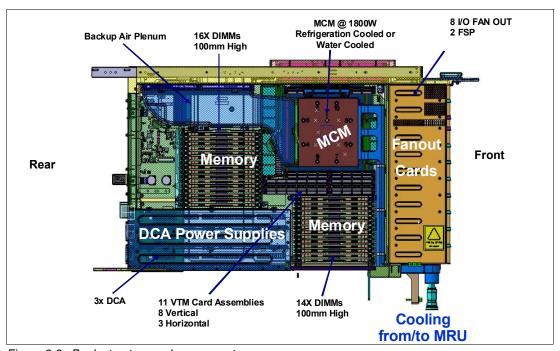

| 2.2 Book concept                                                         |     |

| LL Dook concept                                                          |     |

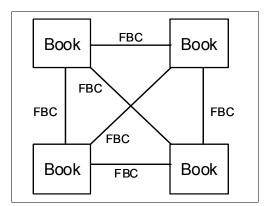

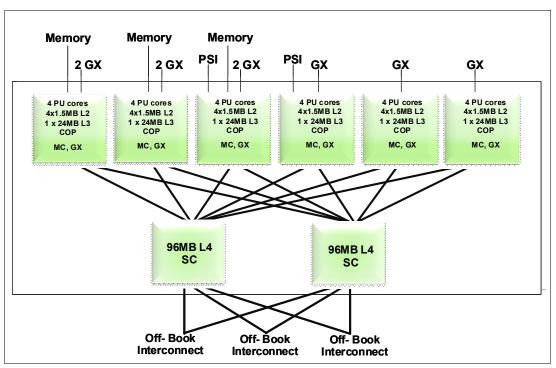

|          | Book interconnect topology                          |    |

|----------|-----------------------------------------------------|----|

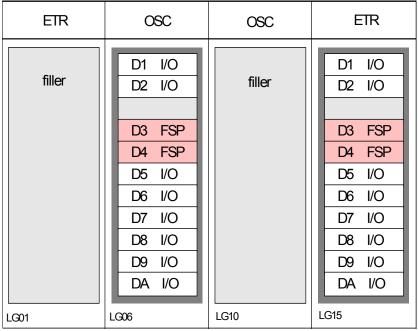

|          | Oscillator                                          |    |

|          | System control                                      |    |

|          | Book power                                          |    |

|          | i-chip module                                       |    |

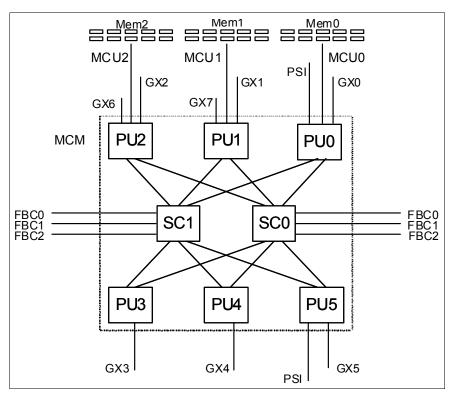

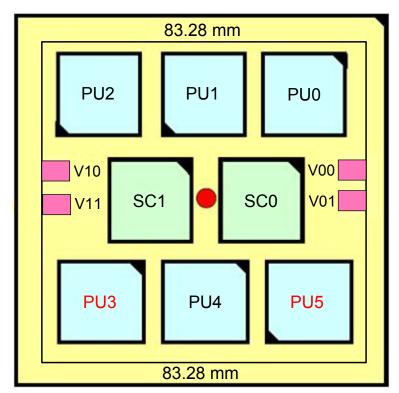

|          | essor units and storage control chips               |    |

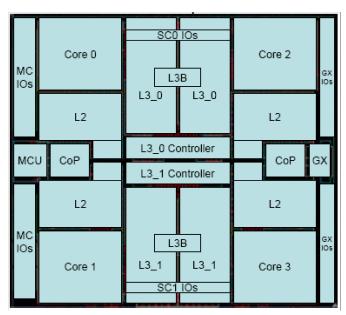

|          | PU chip                                             |    |

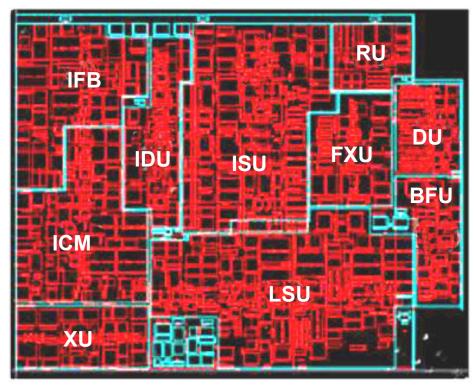

|          | Processor unit (core)                               |    |

|          | PU characterization                                 |    |

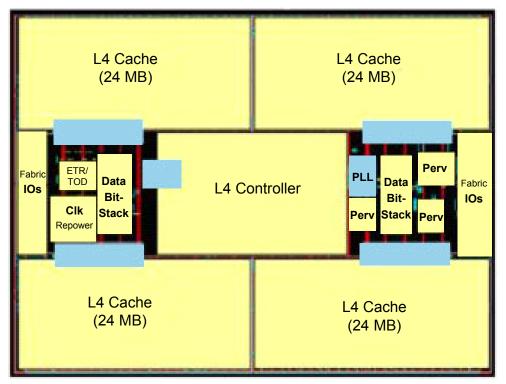

|          | Storage control (SC) chip                           |    |

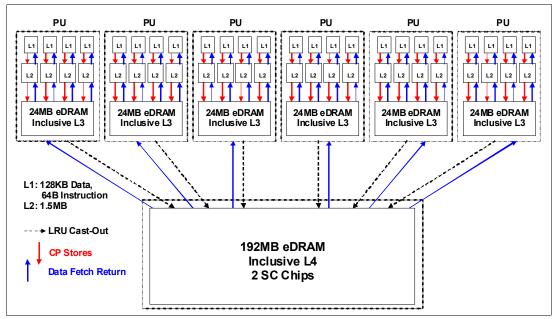

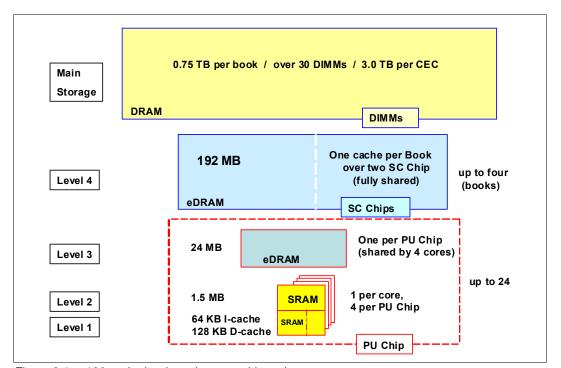

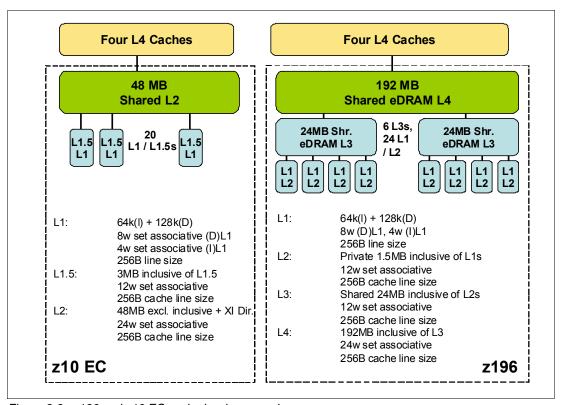

|          | Cache level structure                               |    |

|          | ·                                                   |    |

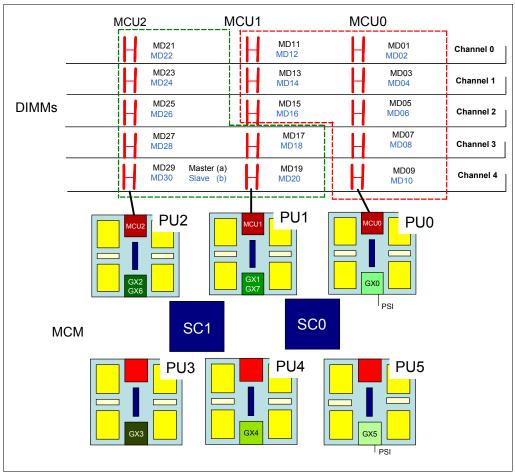

|          | Memory subsystem topology                           |    |

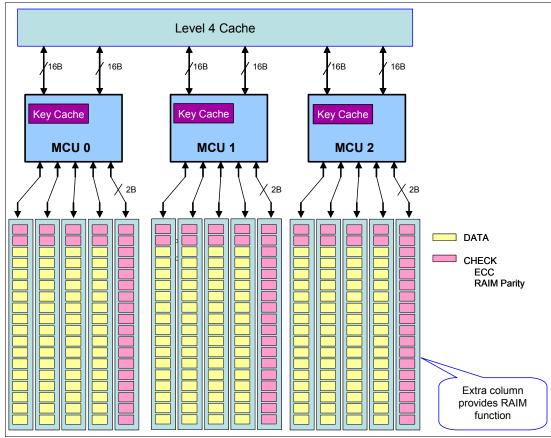

|          | Redundant array of independent memory (RAIM)        |    |

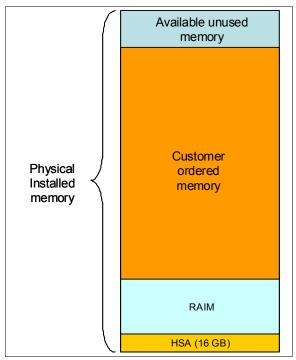

|          | Memory configurations                               |    |

|          | , , ,                                               |    |

|          | Book replacement and memory                         |    |

|          | Flexible Memory Option                              |    |

|          |                                                     |    |

|          | ability, availability, serviceability (RAS)         |    |

|          | nectivity                                           |    |

|          |                                                     |    |

|          | Enhanced book availability                          |    |

|          | Book upgrade                                        |    |

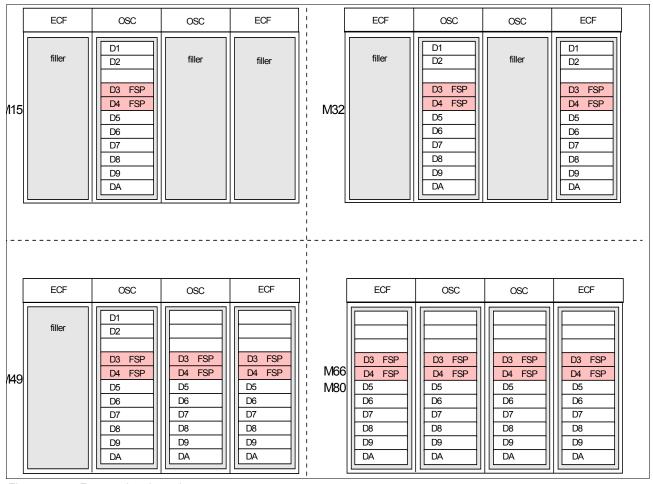

|          | el configurations                                   |    |

|          | Upgrades                                            |    |

|          |                                                     |    |

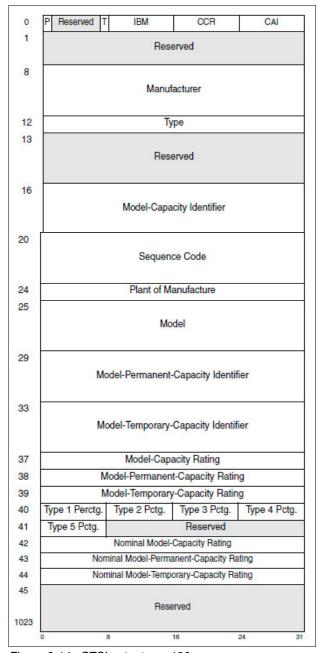

|          | Model capacity identifier                           |    |

|          | Capacity Backup                                     |    |

|          | On/Off Capacity on Demand and CPs                   |    |

|          | er and cooling                                      |    |

|          | Power consumption                                   |    |

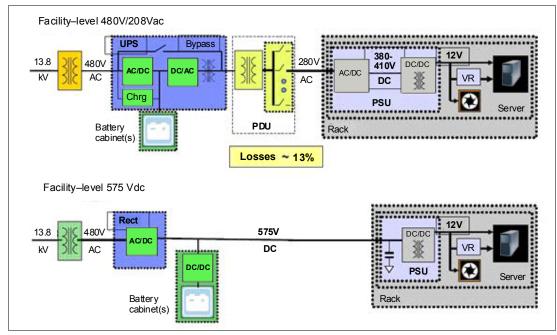

|          | High voltage DC power                               |    |

|          | Internal Battery Feature (IBF)                      |    |

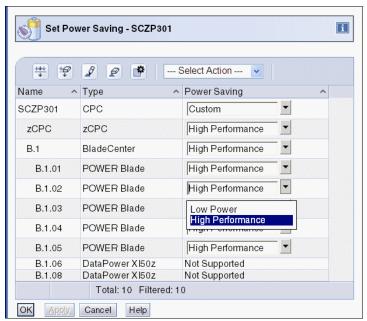

|          | Power capping and power saving                      |    |

|          | Power estimation tool                               |    |

|          | Cooling                                             |    |

|          | Air cooled models                                   |    |

|          | Water cooled models                                 |    |

|          | mmary of z196 structure                             |    |

| 2.10 Sui | illiary of 2190 Structure                           | U9 |

| Chapter  | 3. CPC system design                                | 71 |

| -        | gn highlights                                       |    |

|          | c design                                            |    |

|          | Cache levels and memory structure                   |    |

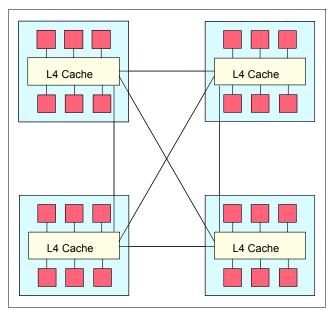

|          | Book interconnect topology                          |    |

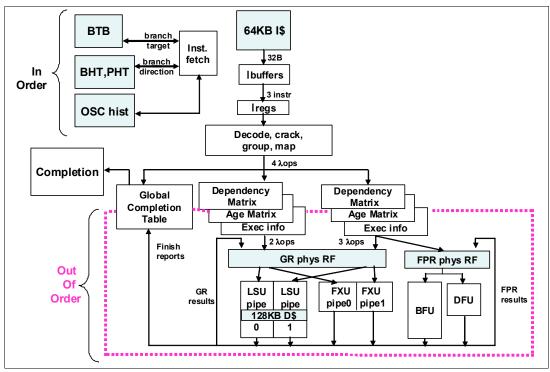

|          | essor unit design                                   |    |

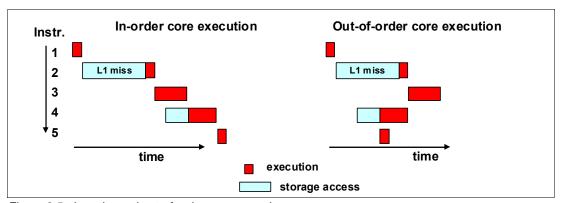

|          | Out-of-order execution                              |    |

|          | Superscalar processor                               |    |

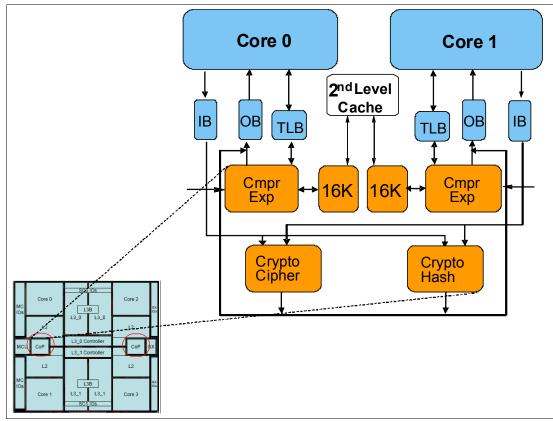

|          | Compression and cryptography accelerators on a chip |    |

|          | Decimal floating point accelerator                  |    |

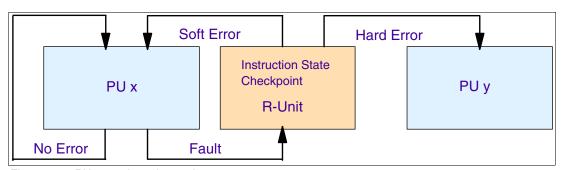

|          | Processor error detection and recovery              |    |

| 3.3.6 Branch prediction                                |       |

|--------------------------------------------------------|-------|

| 3.3.7 Wild branch                                      |       |

| 3.3.8 IEEE floating point                              |       |

| 3.3.9 Translation look-aside buffer                    |       |

| 3.3.10 Instruction fetching, decode, and grouping      |       |

| 3.3.11 Extended translation facility                   |       |

| 3.3.12 Instruction set extensions                      |       |

| 3.4 Processor unit functions                           |       |

| 3.4.1 Overview                                         |       |

| 3.4.2 Central processors                               |       |

| 3.4.3 Integrated Facility for Linux                    |       |

| 3.4.4 Internal Coupling Facility                       |       |

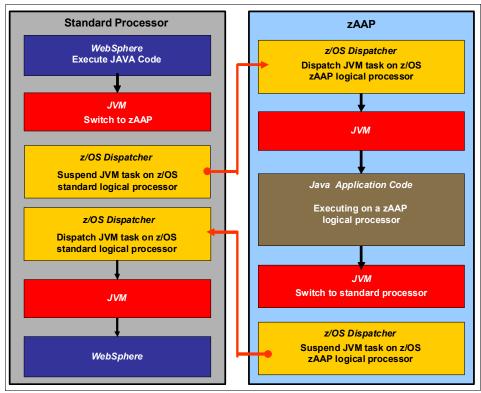

| 3.4.5 System z Application Assist Processors           |       |

| 3.4.6 System z Integrated Information Processor        |       |

| 3.4.7 zAAP on zIIP capability                          |       |

| 3.4.8 System Assist Processors                         |       |

| 3.4.9 Reserved processors                              |       |

| 3.4.10 Processor unit assignment                       | 94    |

| 3.4.11 Sparing rules                                   | 95    |

| 3.4.12 Increased flexibility with z/VM-mode partitions | 95    |

| 3.5 Memory design                                      | 96    |

| 3.5.1 Overview                                         | 96    |

| 3.5.2 Central storage                                  | 98    |

| 3.5.3 Expanded storage                                 | 98    |

| 3.5.4 Hardware system area                             | 99    |

| 3.6 Logical partitioning                               | 99    |

| 3.6.1 Overview                                         | 99    |

| 3.6.2 Storage operations                               | . 105 |

| 3.6.3 Reserved storage                                 |       |

| 3.6.4 Logical partition storage granularity            | . 108 |

| 3.6.5 LPAR dynamic storage reconfiguration             |       |

| 3.7 Intelligent resource director                      |       |

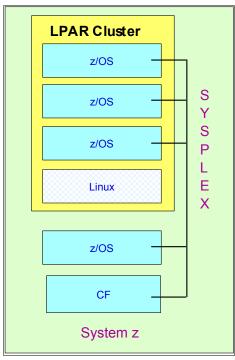

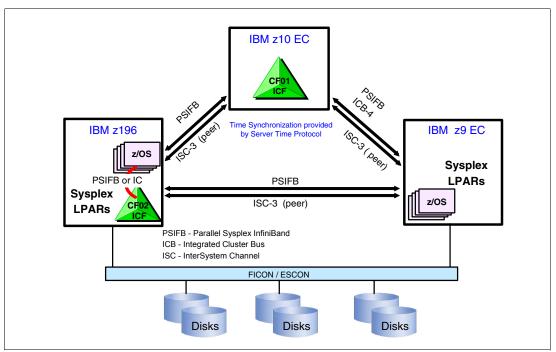

| 3.8 Clustering technology                              |       |

| 3.8.1 Coupling facility control code                   |       |

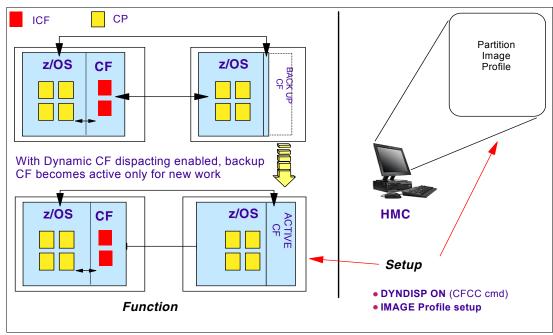

| 3.8.2 Dynamic CF dispatching                           |       |

|                                                        |       |

| Chapter 4. CPC I/O system structure                    | . 115 |

| 4.1 Introduction                                       | 116   |

| 4.1.1 Infrastructure types                             | 116   |

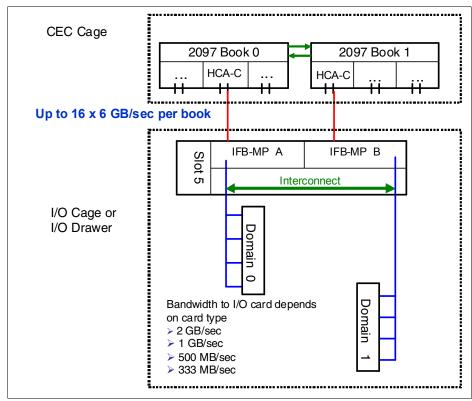

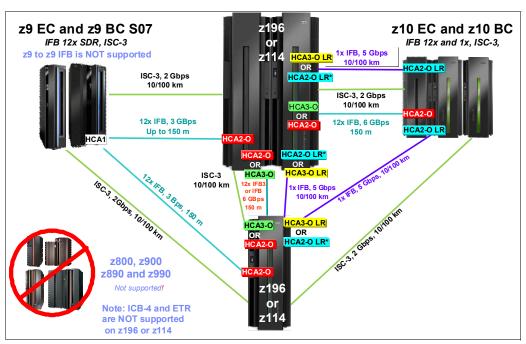

| 4.1.2 InfiniBand specification                         | . 116 |

| 4.1.3 Data, signalling, and link rates                 | 117   |

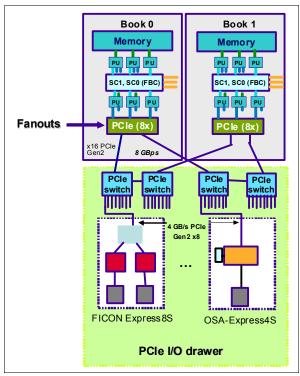

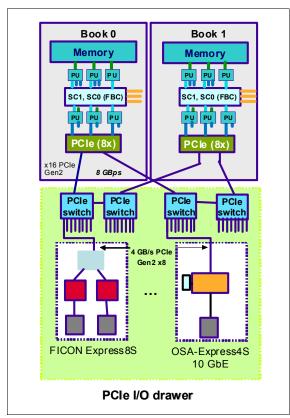

| 4.1.4 PCle                                             |       |

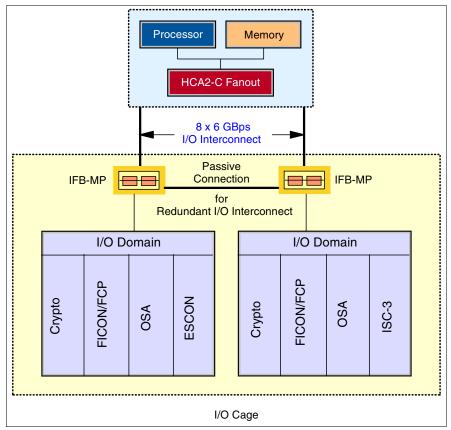

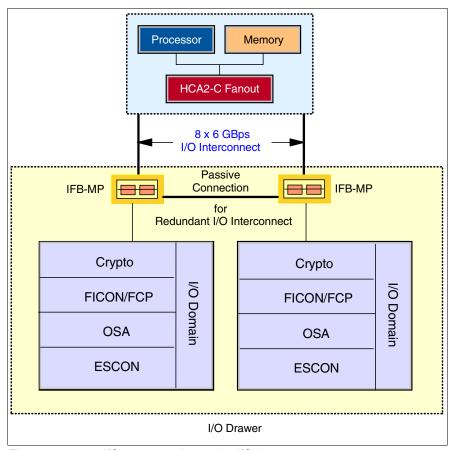

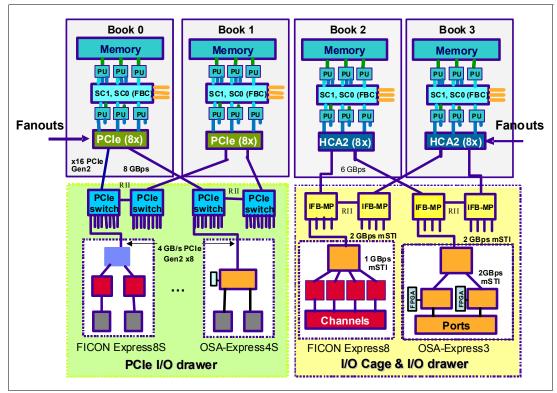

| 4.2 I/O system overview                                | 118   |

| 4.2.1 Characteristics                                  |       |

| 4.2.2 Summary of supported I/O features                | 118   |

| 4.3 I/O cages                                          |       |

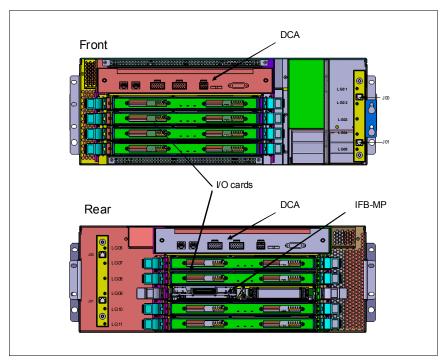

| 4.4 I/O drawers                                        |       |

| 4.5 PCIe I/O drawers.                                  |       |

| 4.6 I/O cage, I/O drawer and PCIe I/O drawer offerings |       |

| 4.7 Fanouts                                            |       |

| 4.7.1 HCA2-C fanout                                    |       |

| 4.7.2 PCIe copper fanout                               |       |

| 4.7.3 HCA2-O (12vIFR) fanout                           | 130   |

| 4.7.4 HCA2-O LR (1xIFB) fanout                                                                     |     |

|----------------------------------------------------------------------------------------------------|-----|

| 4.7.5 HCA3-O (12xIFB) fanout                                                                       |     |

| 4.7.6 HCA3-O LR (1xIFB) fanout                                                                     |     |

| 4.7.7 Fanout considerations                                                                        |     |

| 4.7.8 Fanout summary                                                                               |     |

| 4.8 I/O feature cards                                                                              |     |

| 4.8.1 I/O feature card types ordering information                                                  |     |

| 4.8.2 PCHID report                                                                                 |     |

| 4.9 Connectivity                                                                                   |     |

| 4.9.1 I/O feature support and configuration rules                                                  |     |

| 4.9.2 ESCON channels                                                                               |     |

| 4.9.3 FICON channels                                                                               |     |

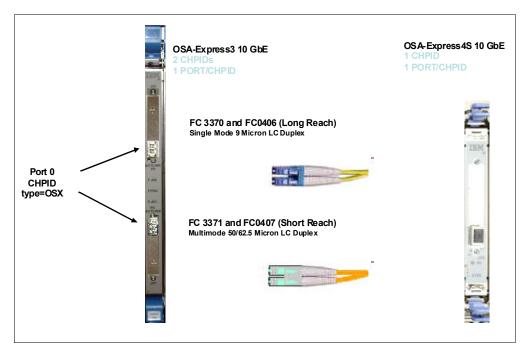

| 4.9.4 OSA-Express4S                                                                                |     |

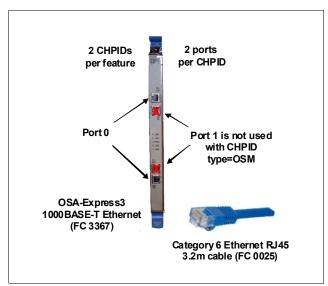

| 4.9.5 OSA-Express3                                                                                 |     |

| 4.9.6 OSA-Express2                                                                                 |     |

| 4.9.7 OSA-Express for ensemble connectivity                                                        |     |

| 4.10 Parallel Sysplex connectivity                                                                 |     |

| 4.10.1 Coupling links                                                                              |     |

| 4.10.2 External clock facility.                                                                    |     |

| 4.11 Cryptographic functions                                                                       |     |

| 4.11.1 CPACF functions (FC 3863)                                                                   |     |

| 4.11.2 Crypto Express3 feature (FC 0864)                                                           |     |

|                                                                                                    |     |

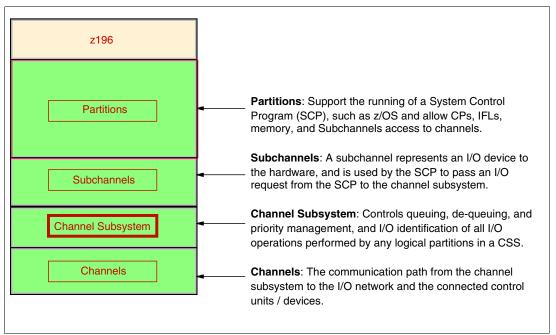

| Chapter 5. CPC channel subsystem                                                                   | 163 |

| 5.1 Channel subsystem                                                                              |     |

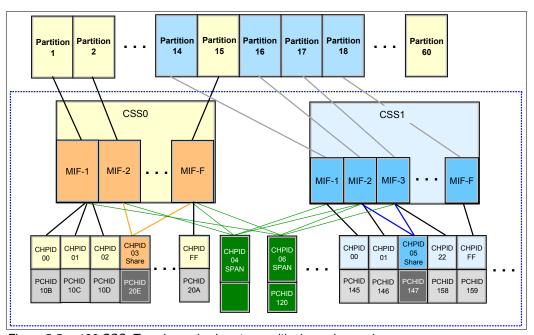

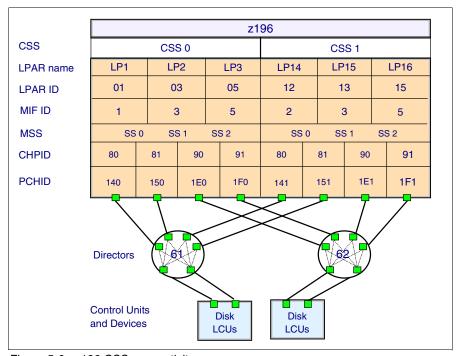

| 5.1.1 Multiple CSSs concept                                                                        |     |

| 5.1.2 CSS elements                                                                                 |     |

| 5.1.3 Multiple subchannel sets                                                                     |     |

| 5.1.4 Parallel access volumes and extended address volumes                                         |     |

| 5.1.5 Logical partition name and identification                                                    |     |

| 5.1.6 Physical channel ID                                                                          |     |

| 5.1.7 Channel spanning                                                                             |     |

| 5.1.8 Multiple CSS construct                                                                       |     |

| 5.1.9 Adapter ID                                                                                   |     |

| 5.2 I/O configuration management                                                                   |     |

| <ul><li>5.3 Channel subsystem summary</li><li>5.4 System-initiated CHPID reconfiguration</li></ul> |     |

| 5.5 Multipath initial program load                                                                 |     |

| 5.5 Wullipati Illitiai program load                                                                | 174 |

| Chapter 6. Cryptography                                                                            | 175 |

| 6.1 Cryptographic synchronous functions                                                            |     |

| 6.2 Cryptographic asynchronous functions                                                           | 176 |

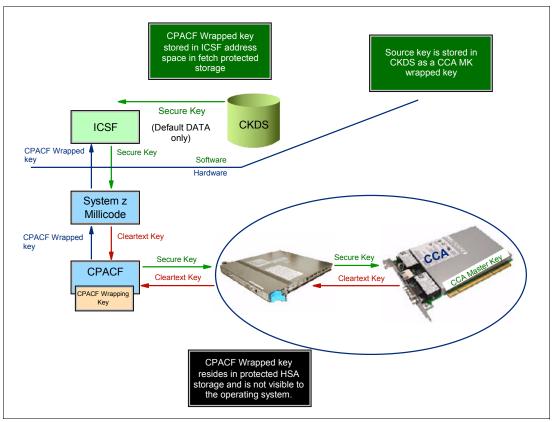

| 6.2.1 Secure key functions                                                                         |     |

| 6.2.2 CPACF protected key                                                                          | 177 |

| 6.2.3 Other key functions                                                                          | 179 |

| 6.2.4 Cryptographic feature codes                                                                  | 180 |

| 6.3 CP Assist for Cryptographic Function                                                           | 181 |

| 6.4 Crypto Express3                                                                                |     |

| 6.4.1 Crypto Express3 coprocessor                                                                  |     |

| 6.4.2 Crypto Express3 accelerator                                                                  |     |

| 6.4.3 Configuration rules                                                                          |     |

| 6.5 TKE workstation feature                                                                        | 188 |

| 6.5.1 Logical partition, TKE host, and TKE target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 191<br>192                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| ••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

| Chapter 7. zEnterprise BladeCenter Extension Model 002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |

| 7.1 zBX concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

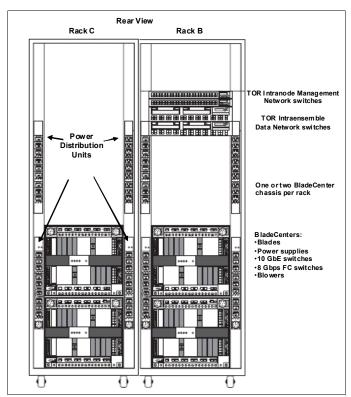

| 7.2.1 zBX racks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

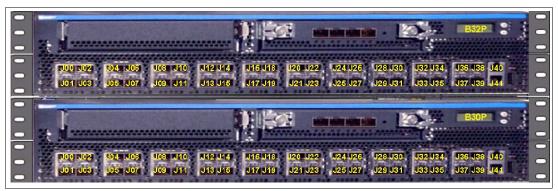

| 7.2.2 Top of rack (TOR) switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

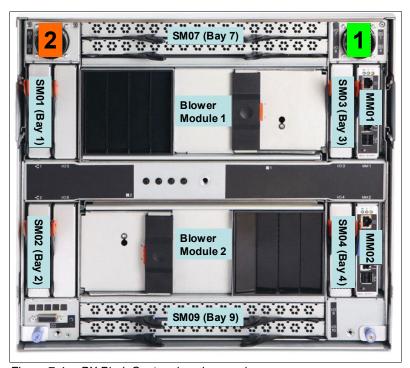

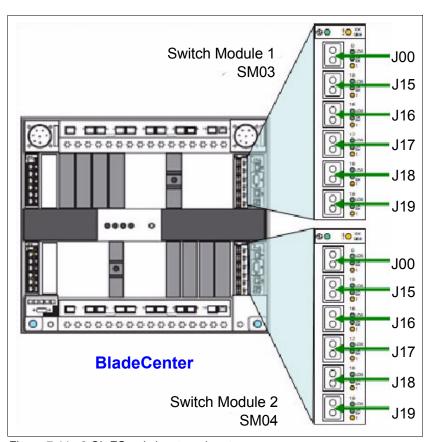

| 7.2.3 zBX BladeCenter chassis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

| 7.2.4 zBX blades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |

| 7.2.5 Power distribution unit (PDU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

| 7.3 zBX entitlements and firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |

| 7.3.1 zBX management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

| 7.3.2 zBX firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

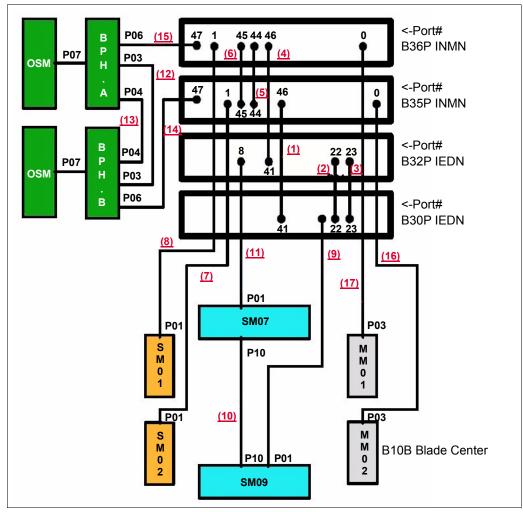

| 7.4 zBX connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |

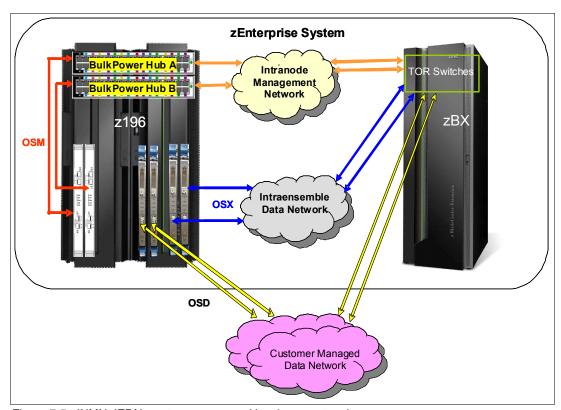

| 7.4.1 Intranode management network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

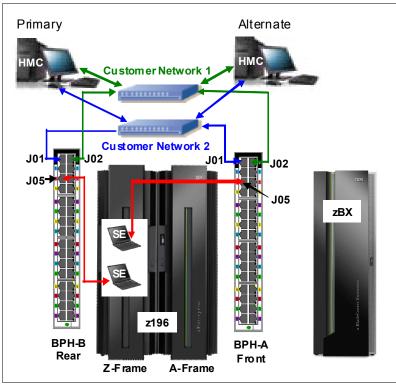

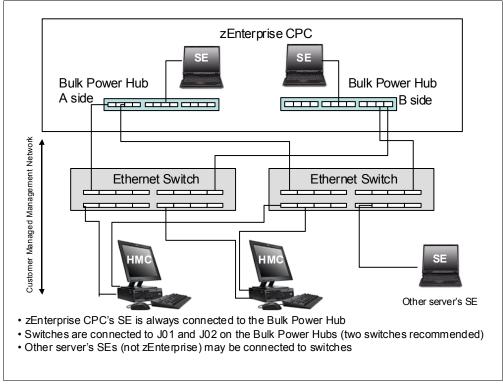

| 7.4.2 Primary and alternate HMCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 213                                                         |

| 7.4.3 Intraensemble data network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 214                                                         |

| 7.4.4 Network connectivity rules with zBX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 217                                                         |

| 7.4.5 Network security considerations with zBX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 217                                                         |

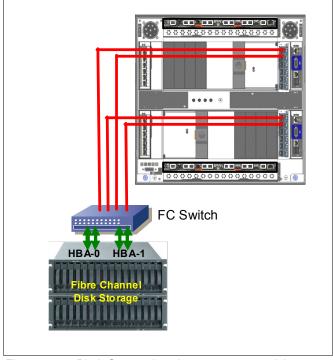

| 7.4.6 zBX storage connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 219                                                         |

| 7.5 zBX connectivity examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

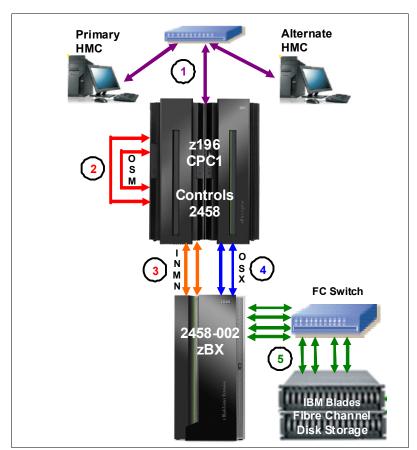

| 7.5.1 A single node ensemble with a zBX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 221                                                         |

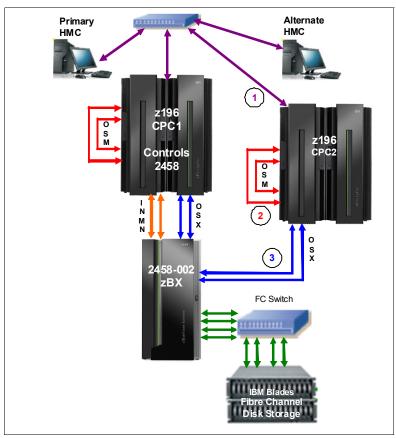

| 7.5.2 A dual node ensemble with a single zBX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

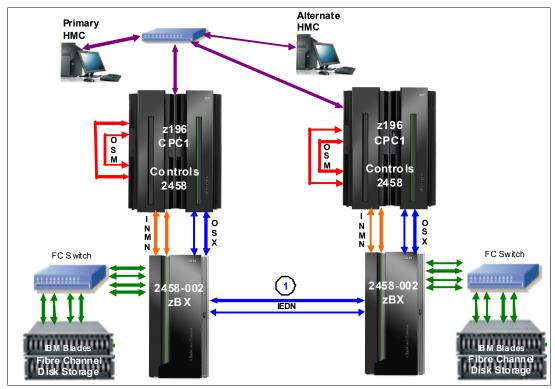

| 7.5.3 A dual node ensemble with two zBXs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 004                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                             |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225                                                         |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225                                                         |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225<br>227<br>228                                           |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225 227 228                                                 |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225 227 228 228                                             |

| 7.6 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 225 227 228 228 229                                         |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 225 227 228 229 229                                         |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 225 227 228 228 229 229                                     |

| 7.6 References  Chapter 8. Software support 8.1 Operating systems summary 8.2 Support by operating system 8.2.1 z/OS 8.2.2 z/VM 8.2.3 z/VSE 8.2.4 z/TPF                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 225 227 228 228 229 229 229                                 |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.                                                                                                                                                                                                                                                                                                                                                                                                                        | 225 227 228 229 229 229 229                                 |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image.                                                                                                                                                                                                                                                                                                                             | 225 227 228 229 229 229 230 240                             |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support                                                                                                                                                                                                                                                                                                           | 225 227 228 229 229 229 230 240 241                         |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support                                                                                                                                                                                                                                                                                      | 225 227 228 229 229 229 230 240 241                         |

| 7.6 References  Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability                                                                                                                                                                                                                                                       | 225 227 228 229 229 229 229 240 241 242                     |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size                                                                                                                                                                                                                                      | 225 227 228 229 229 229 230 240 241 242 243                 |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support                                                                                                                                                                                                             | 225 227 228 229 229 229 230 240 241 242 243 243             |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image.  8.3.2 zAAP support  8.3.3 zIIP support.  8.3.4 zAAP on zIIP capability.  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility                                                                                                                                                    | 225 227 228 229 229 229 240 241 242 243 243                 |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility  8.3.8 Hardware decimal floating point                                                                                                                | 225 227 228 229 229 229 240 241 242 243 243                 |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility  8.3.8 Hardware decimal floating point  8.3.9 Up to 60 logical partitions                                                                              | 225 227 228 229 229 229 240 241 242 243 243 244             |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility  8.3.8 Hardware decimal floating point  8.3.9 Up to 60 logical partitions  8.3.10 Separate LPAR management of PUs                                      | 225 227 228 229 229 229 230 240 241 242 243 243 244 244     |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z.  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility  8.3.8 Hardware decimal floating point  8.3.9 Up to 60 logical partitions  8.3.10 Separate LPAR management of PUs  8.3.11 Dynamic LPAR memory upgrade | 225 227 228 229 229 229 230 240 241 242 243 244 244 244     |

| Chapter 8. Software support  8.1 Operating systems summary  8.2 Support by operating system  8.2.1 z/OS  8.2.2 z/VM  8.2.3 z/VSE  8.2.4 z/TPF  8.2.5 Linux on System z  8.2.6 z196 functions support summary  8.3 Support by function  8.3.1 Single system image  8.3.2 zAAP support  8.3.3 zIIP support  8.3.4 zAAP on zIIP capability  8.3.5 Maximum main storage size  8.3.6 Large page support  8.3.7 Guest support for execute-extensions facility  8.3.8 Hardware decimal floating point  8.3.9 Up to 60 logical partitions  8.3.10 Separate LPAR management of PUs                                      | 225 227 228 229 229 229 240 241 242 243 243 244 244 244 244 |

vii

| 8.3.15 The 63.75 K subchannels                                            | 246 |

|---------------------------------------------------------------------------|-----|

| 8.3.16 Multiple subchannel sets                                           |     |

| 8.3.17 Third subchannel set                                               |     |

| 8.3.18 IPL from an alternate subchannel set                               |     |

| 8.3.19 MIDAW facility                                                     |     |

| 8.3.20 Enhanced CPACF                                                     |     |

| 8.3.21 HiperSockets multiple write facility                               |     |

| 8.3.22 HiperSockets IPv6                                                  |     |

| 8.3.23 HiperSockets Layer 2 support                                       |     |

|                                                                           |     |

| 8.3.24 HiperSockets network traffic analyzer for Linux on System z        |     |

| 8.3.25 HiperSockets statements of direction                               |     |

| 8.3.26 FICON Express8S                                                    |     |

| 8.3.27 FICON Express8                                                     |     |

| 8.3.28 z/OS discovery and autoconfiguration (zDAC)                        |     |

| 8.3.29 High performance FICON (zHPF)                                      |     |

| 8.3.30 Request node identification data                                   |     |

| 8.3.31 Extended distance FICON                                            |     |

| 8.3.32 Platform and name server registration in FICON channel             |     |

| 8.3.33 FICON link incident reporting                                      |     |

| 8.3.34 FCP provides increased performance                                 |     |

| 8.3.35 N_Port ID virtualization                                           |     |

| 8.3.36 OSA-Express4S 10 Gigabit Ethernet LR and SR                        |     |

| 8.3.37 OSA-Express4S Gigabit Ethernet LX and SX                           | 255 |

| 8.3.38 OSA-Express3 10 Gigabit Ethernet LR and SR                         | 256 |

| 8.3.39 OSA-Express3 Gigabit Ethernet LX and SX                            | 256 |

| 8.3.40 OSA-Express3 1000BASE-T Ethernet                                   | 257 |

| 8.3.41 OSA-Express2 1000BASE-T Ethernet                                   | 258 |

| 8.3.42 Open Systems Adapter for Ensemble                                  | 259 |

| 8.3.43 Intranode management network (INMN)                                | 259 |

| 8.3.44 Intraensemble data network (IEDN)                                  | 259 |

| 8.3.45 OSA-Express3 and OSA-Express2 NCP support (OSN)                    |     |

| 8.3.46 Integrated Console Controller                                      |     |

| 8.3.47 VLAN management enhancements                                       |     |

| 8.3.48 GARP VLAN Registration Protocol                                    |     |

| 8.3.49 Inbound workload queueing (IWQ) for OSA-Express4S and OSA-Express3 |     |

| 8.3.50 Inbound workload queueing (IWQ) for Enterprise Extender            |     |

| 8.3.51 Query and display OSA configuration                                |     |

| 8.3.52 Link aggregation support for z/VM                                  |     |

| 8.3.53 QDIO data connection isolation for z/VM                            |     |

| 8.3.54 QDIO interface isolation for z/OS                                  |     |

| 8.3.55 QDIO optimized latency mode                                        |     |

| 8.3.56 OSA-Express4S checksum offload                                     |     |

| 8.3.57 Checksum offload for IPv4 packets when in QDIO mode                |     |

| 8.3.58 Adapter interruptions for QDIO                                     |     |

| 8.3.59 OSA Dynamic LAN idle                                               |     |

| 8.3.60 OSA Layer 3 Virtual MAC for z/OS environments                      |     |

| 8.3.61 QDIO Diagnostic Synchronization.                                   |     |

| 8.3.62 Network Traffic Analyzer                                           |     |

| 8.3.63 Program directed re-IPL                                            |     |

| 8.3.64 Coupling over InfiniBand                                           |     |

| 8.3.65 Dynamic I/O support for InfiniBand CHPIDs                          |     |

| 8.4 Cryptographic support                                                 |     |

| 8.4.1 CP Assist for Cryptographic Function                                |     |

| 0.7.1 OI Assist for Oryptographile Function                               | 207 |

| 8.4.2 Crypto Express3                                                     |     |

|---------------------------------------------------------------------------|-----|

| 8.4.3 Web deliverables                                                    | 268 |

| 8.4.4 z/OS ICSF FMIDs                                                     | 269 |

| 8.4.5 ICSF migration considerations                                       | 272 |

| 8.5 z/OS migration considerations                                         |     |

| 8.5.1 General guidelines                                                  |     |

| 8.5.2 HCD                                                                 |     |

| 8.5.3 InfiniBand coupling links                                           | 273 |

| 8.5.4 Large page support                                                  | 273 |

| 8.5.5 HiperDispatch                                                       |     |

| 8.5.6 Capacity Provisioning Manager                                       | 274 |

| 8.5.7 Decimal floating point and z/OS XL C/C++ considerations             |     |

| 8.6 Coupling facility and CFCC considerations                             | 275 |

| 8.7 MIDAW facility                                                        | 276 |

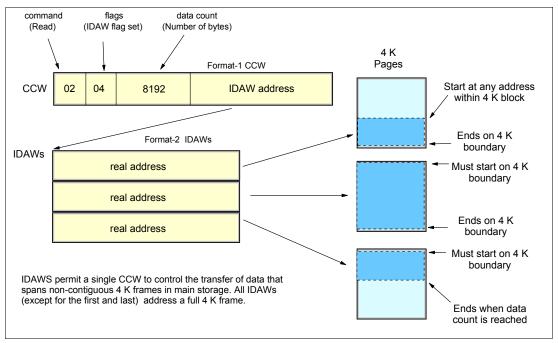

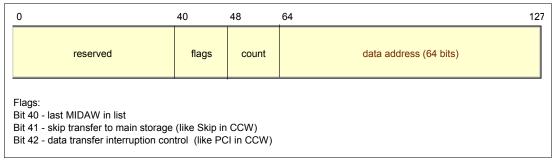

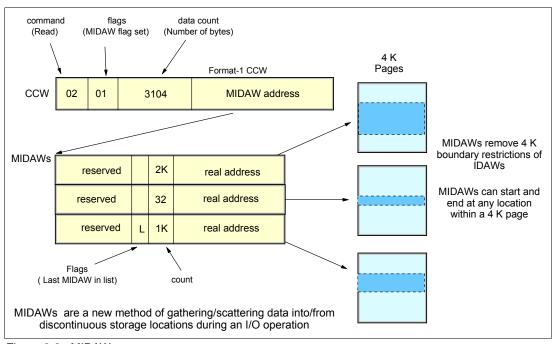

| 8.7.1 MIDAW technical description                                         | 277 |

| 8.7.2 Extended format data sets                                           | 279 |

| 8.7.3 Performance benefits                                                | 279 |

| 8.8 IOCP                                                                  | 280 |

| 8.9 Worldwide portname (WWPN) tool                                        |     |

| 8.10 ICKDSF                                                               | 281 |

| 8.11 zEnterprise BladeCenter Extension software support                   | 281 |

| 8.11.1 IBM Blades                                                         | 281 |

| 8.11.2 IBM WebSphere DataPower Integration Appliance XI50 for zEnterprise | 282 |

| 8.11.3 IBM Smart Analytics Optimizer solution                             | 282 |

| 8.12 Software licensing considerations                                    | 283 |

| 8.12.1 MLC pricing metrics                                                | 283 |

| 8.12.2 Advanced Workload License Charges (AWLC)                           | 285 |

| 8.12.3 Advanced Entry Workload License Charges (AEWLC)                    | 285 |

| 8.12.4 System z New Application License Charges (zNALC)                   | 285 |

| 8.12.5 Select Application License Charges (SALC)                          | 286 |

| 8.12.6 Midrange Workload Licence Charges (MWLC)                           | 286 |

| 8.12.7 Parallel Sysplex Licence Charges (PWLC)                            |     |

| 8.12.8 System z International Program License Agreement (IPLA)            | 287 |

| 8.13 References                                                           | 288 |

|                                                                           |     |

| Chapter 9. System upgrades                                                |     |

| 9.1 Upgrade types                                                         |     |

| 9.1.1 Overview                                                            |     |

| 9.1.2 Permanent upgrades                                                  |     |

| 9.1.3 Temporary upgrades                                                  |     |

| 9.2 Concurrent upgrades                                                   |     |

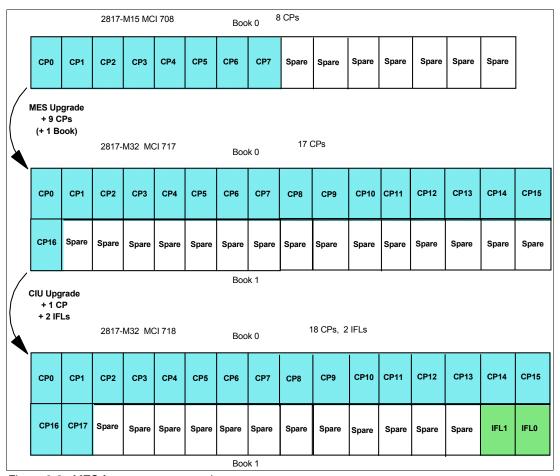

| 9.2.1 Model upgrades                                                      |     |

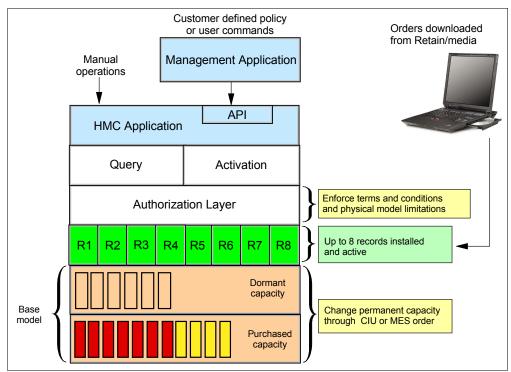

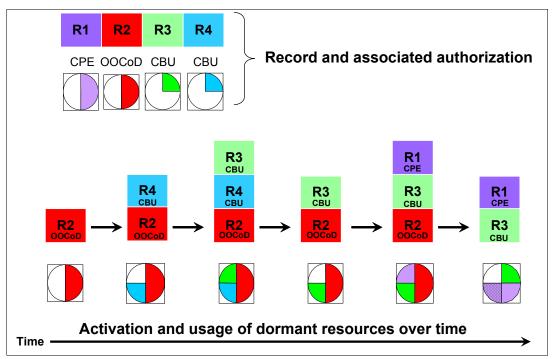

| 9.2.2 Customer Initiated Upgrade facility                                 |     |

| , , , ,                                                                   | 301 |

| 9.3 MES upgrades                                                          |     |

| 9.3.1 MES upgrade for processors                                          |     |

| 9.3.2 MES upgrades for memory                                             |     |

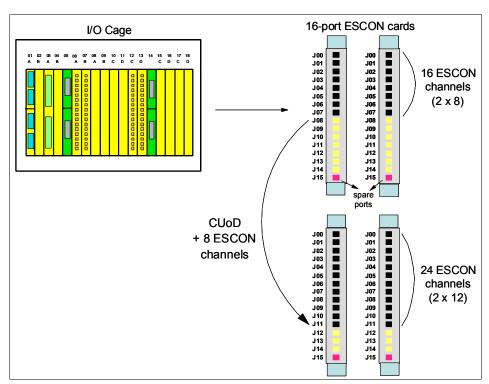

| 9.3.3 MES upgrades for I/O                                                |     |

| 9.3.4 MES upgrades for the zBX                                            |     |

| 9.3.5 Plan-ahead concurrent conditioning                                  |     |

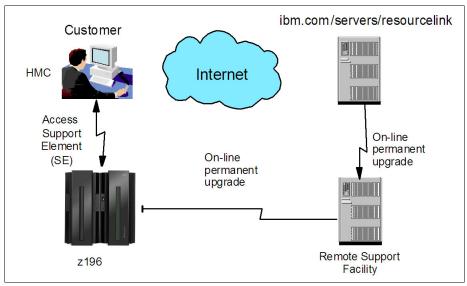

| 9.4 Permanent upgrade through the CIU facility                            |     |

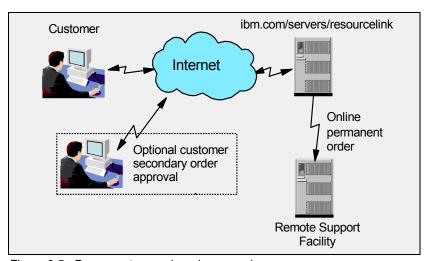

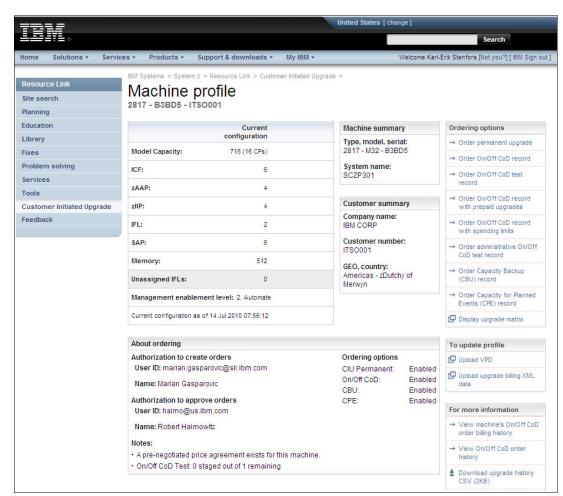

| 9.4.1 Ordering                                                            |     |

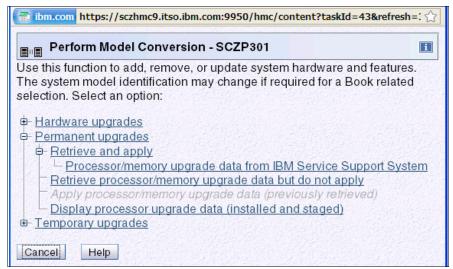

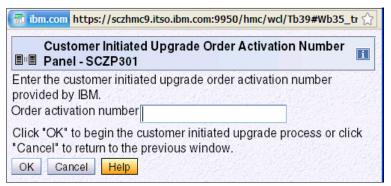

| 9.4.2 Retrieval and activation                                            | 309 |

| 9.5 On/Off Capacity on Demand                        |     |

|------------------------------------------------------|-----|

| 9.5.1 Overview                                       |     |

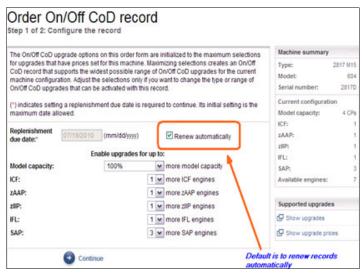

| 9.5.2 Ordering                                       |     |

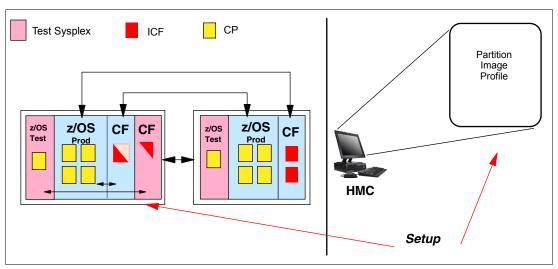

| 9.5.3 On/Off CoD testing                             |     |

| 9.5.4 Activation and deactivation                    |     |

| 9.5.5 Termination                                    |     |

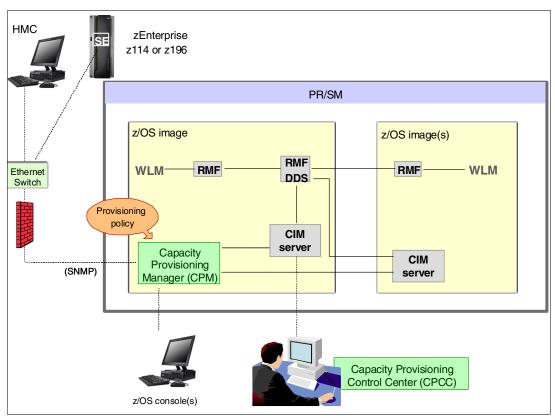

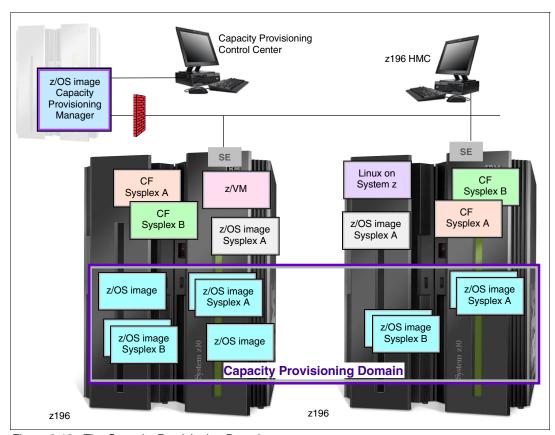

| 9.5.6 z/OS capacity provisioning                     |     |

| 9.6 Capacity for Planned Event                       |     |

| 9.7 Capacity Backup                                  |     |

| 9.7.1 Ordering                                       |     |

| 9.7.2 CBU activation and deactivation                |     |

| 9.7.3 Automatic CBU enablement for GDPS              |     |

| 9.8 Nondisruptive upgrades                           |     |

| 9.8.1 Components                                     |     |

| 9.8.2 Concurrent upgrade considerations              |     |

| 9.9 Summary of Capacity on Demand offerings          |     |

| 9.10 References                                      | 333 |

| Chapter 10. RAS                                      | 335 |

| 10.1 z196 availability characteristics               |     |

| 10.2 z196 RAS functions                              |     |

| 10.2.1 Scheduled outages                             |     |

| 10.2.2 Unscheduled outages                           |     |

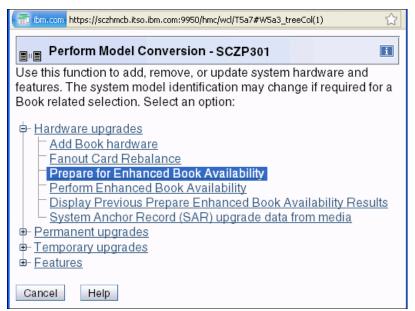

| 10.3 z196 Enhanced book availability                 |     |

| 10.3.1 EBA planning considerations                   |     |

| 10.3.2 Enhanced book availability processing         |     |

| 10.4 z196 Enhanced driver maintenance                |     |

| 10.5 RAS capability for the HMC in an ensemble       |     |

| 10.6 RAS capability for zBX                          |     |

| 10.6.1 BladeCenter components                        |     |

| 10.6.2 zBX firmware                                  |     |

| 10.6.3 zBX RAS and the Unified Resource Manager      |     |

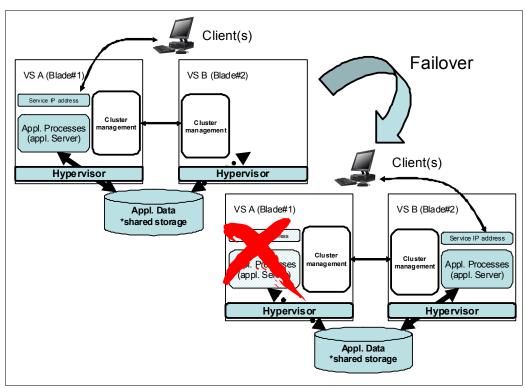

| 10.7 Considerations for PowerHA in zBX environment.  |     |

| To./ Considerations for Fower IA in 2DX environment. | 551 |

| Chapter 11. Environmental requirements               | 353 |

| 11.1 z196 power and cooling                          | 354 |

| 11.1.1 Power consumption                             | 354 |

| 11.1.2 Internal Battery Feature                      | 355 |

| 11.1.3 Emergency power-off                           | 356 |

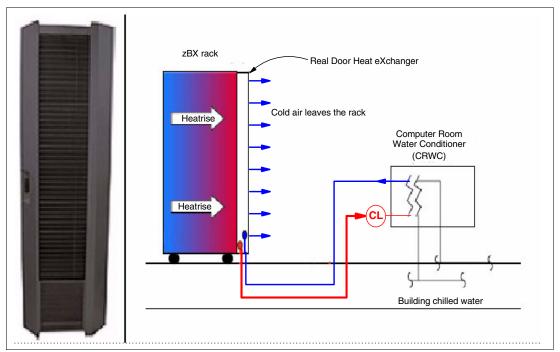

| 11.1.4 Cooling requirements                          | 356 |

| 11.2 z196 physical specifications                    | 357 |

| 11.2.1 Weights and dimensions                        | 357 |

| 11.2.2 Weight distribution plate                     | 357 |

| 11.2.3 3-in-1 bolt down kit for raised floor         | 358 |

| 11.3 zBX environmentals                              | 358 |

| 11.3.1 zBX configurations                            | 358 |

| · · · · · · · · · · · · · · · · · · ·                | 359 |

|                                                      | 360 |

|                                                      | 362 |

| · ·                                                  | 363 |

| · · · · · · · · · · · · · · · · · · ·                | 364 |

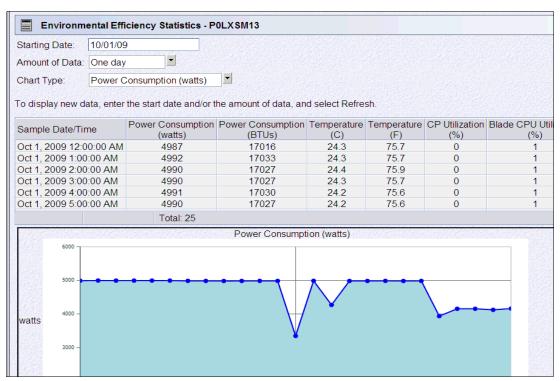

| 11.4.2 Query maximum potential power                 | 364 |

| · · · · · · · · · · · · · · · · · · ·                | 365 |

| 65         |

|------------|

| 66         |

| •          |

| 69         |

| 70         |

| 70         |

| 71         |

| 71         |

| 74         |

|            |

| 74         |

| 75         |

| 76         |

| 76         |

| 76         |

| 77         |

| 77         |

| 77         |

| 78         |

| 78         |

| 78         |

| 79         |

|            |

| 81         |

| 82         |

| 83         |

| 84         |

| 85         |

| 85         |

| 86         |

| 86         |

| 87         |

| 87         |

| 87         |

| 88         |

| 90         |

| 92         |

| 92         |

|            |

| 92         |

| 93         |

| 95         |

| 90         |

| 99         |

| 99         |

| 99         |

| J          |

|            |

| 00         |

| .00<br>.01 |

| 00         |

|            |

# **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive, Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM websites are provided for convenience only and do not in any manner serve as an endorsement of those websites. The materials at those websites are not part of the materials for this IBM product and use of those websites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### **COPYRIGHT LICENSE:**

This information contains sample application programs in source language, which illustrate programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs.

#### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation in the United States, other countries, or both. These and other IBM trademarked terms are marked on their first occurrence in this information with the appropriate symbol (® or ™), indicating US registered or common law trademarks owned by IBM at the time this information was published. Such trademarks may also be registered or common law trademarks in other countries. A current list of IBM trademarks is available on the Web at http://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

1-2-3® IBM Systems Director Active Energy Redbooks (logo) @® **AIX®** Manager™ Resource Link™ BladeCenter® **IBM®** Resource Measurement Facility™ IMS™ **CICS® RETAIN®** Language Environment® RMF™ DataPower® DB2 Connect™ **Lotus®** Sysplex Timer® DB2® **MQSeries®** System p® System Storage® Distributed Relational Database Parallel Sysplex® Architecture™ Passport Advantage® System x® Domino® Power Systems™ System z10® POWER6® **DRDA®** System z9® POWER7™ System z® DS8000® ECKD™ PowerHA™ **Tivoli® ESCON®** PowerPC® WebSphere® **FICON®** PowerVM™ z/Architecture® FlashCopy® **POWER®** z/OS® **GDPS®** PR/SM<sup>TM</sup> z/VM® Geographically Dispersed Parallel Processor Resource/Systems z/VSETM z10™ Sysplex<sup>™</sup> Manager™ НАСМР™ **RACF® z9**® HiperSockets™ Redbooks® zSeries®

Intel, Intel logo, Intel Inside logo, and Intel Centrino logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Microsoft, Windows NT, Windows, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java, and all Java-based trademarks and logos are trademarks or registered trademarks of Oracle and/or its affiliates.

UNIX is a registered trademark of The Open Group in the United States and other countries.

Other company, product, or service names may be trademarks or service marks of others.

# **Preface**

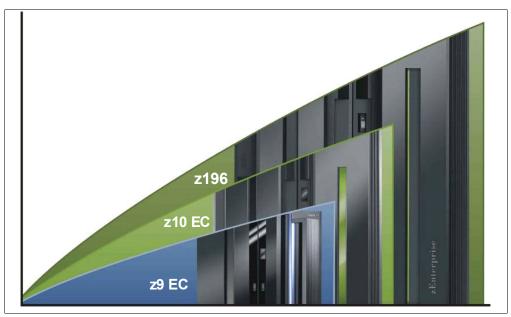

The popularity of the Internet and the affordability of IT hardware and software have resulted in an explosion of applications, architectures, and platforms. Workloads have changed. Many applications, including mission-critical ones, are deployed on a variety of platforms, and the System z® design has adapted to this change. It takes into account a wide range of factors, including compatibility and investment protection, to match the IT requirements of an enterprise.

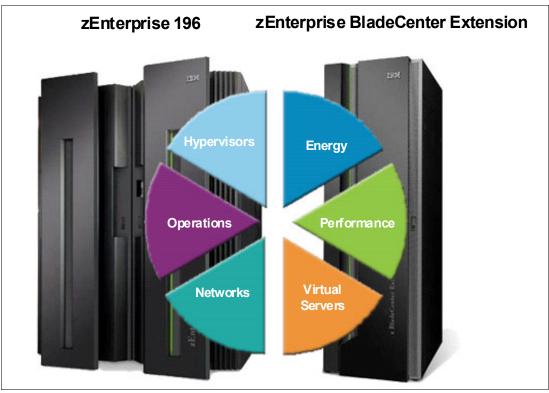

This IBM® Redbooks® publication discusses the IBM zEnterprise System, an IBM scalable mainframe server. IBM is taking a revolutionary approach by integrating different platforms under the well-proven System z hardware management capabilities, while extending System z qualities of service to those platforms.

The zEnterprise System consists of the IBM zEnterprise 196 central processor complex, the IBM zEnterprise Unified Resource Manager, and the IBM zEnterprise BladeCenter® Extension. The z196 is designed with improved scalability, performance, security, resiliency, availability, and virtualization.

The z196 Model M80 provides up to 1.6 times the total system capacity of the z10<sup>TM</sup> EC Model E64, and all z196 models provide up to twice the available memory of the z10 EC. The zBX infrastructure works with the z196 to enhance System z virtualization and management through an integrated hardware platform that spans mainframe, POWER7<sup>TM</sup>, and System x® technologies. Through the Unified Resource Manager, the zEnterprise System is managed as a single pool of resources, integrating system and workload management across the environment.

This book provides an overview of the zEnterprise System and its functions, features, and associated software support. Greater detail is offered in areas relevant to technical planning. This book is intended for systems engineers, consultants, planners, and anyone wanting to understand the zEnterprise System functions and plan for their usage. It is not intended as an introduction to mainframes. Readers are expected to be generally familiar with existing IBM System z technology and terminology.

## The team who wrote this book

This book was produced by a team of specialists from around the world working at the International Technical Support Organization, Poughkeepsie Center.

**Bill White** is a Project Leader and Senior System z Networking and Connectivity Specialist at the International Technical Support Organization, Poughkeepsie Center.

**Erik Bakker** is a Senior IT Specialist working for IBM Server and Technology Group in the Netherlands. During the past 24 years he has worked in various roles within IBM and with a large number of mainframe customers. For many years he worked for Global Technology Services as a systems programmer providing implementation and consultancy services at many customer sites. He currently provides pre-sales System z technical consultancy in support of large and small System z customers. His areas of expertise include Parallel Sysplex®, z/OS®, and System z.

Parwez Hamid is an Executive IT Consultant working for the IBM Server and Technology Group. During the past 37 years he has worked in various IT roles within IBM. Since 1988 he has worked with a large number of IBM mainframe customers and spent much of his time introducing new technology. Currently, he provides pre-sales technical support for the IBM System z product portfolio and is the lead System z technical specialist for UK and Ireland. Parwez co-authors a number of Redbooks publications and prepares technical material for the world-wide announcement of System z Servers. Parwez works closely with System z product development in Poughkeepsie and provides input and feedback for future product plans. Additionally, Parwez is a member of the IBM IT Specialist profession certification board in the UK and is also a Technical Staff member of the IBM UK Technical Council which is made of senior technical specialist representing all of the IBM Client, Consulting, Services, and Product groups. Parwez teaches and presents at numerous IBM user group and IBM internal conferences.

**Octavian Lascu** is a Project Leader and Senior IT Specialist at the International Technical Support Organization, Poughkeepsie Center.

Fernando Nogal is an IBM Certified Consulting IT Specialist working as an STG Technical Consultant for the Spain, Portugal, Greece, and Israel IMT. He specializes in on-demand infrastructures and architectures. In his 28 years with IBM, he has held a variety of technical positions, mainly providing support for mainframe customers. Previously, he was on assignment to the Europe Middle East and Africa (EMEA) zSeries® Technical Support group, working full time on complex solutions for e-business on zSeries. His job included, and still does, presenting and consulting in architectures and infrastructures, and providing strategic guidance to System z customers regarding the establishment and enablement of e-business technologies on System z, including the z/OS, z/VM®, and Linux environments. He is a zChampion and a core member of the System z Business Leaders Council. An accomplished writer, he has authored and co-authored over 20 Redbooks publications and several technical papers. Other activities include chairing a Virtual Team from IBM interested in e-business on System z, and serving as a University Ambassador. He travels extensively on direct customer engagements and as a speaker at IBM and customer events and trade shows.