# IBM eserver zSeries 990 Technical Introduction

ibm.com/redbooks

Redbooks

International Technical Support Organization

IBM @server zSeries 990 Technical Introduction

May 2003

Note: Before using this information and the product it supports, read the information in "Notices" on page vii.

#### First Edition (May 2003)

This edition applies to the announcement of the IBM @server zSeries 990 system.

# **Contents**

| Trademarks                                  |    |

|---------------------------------------------|----|

| Preface                                     | is |

| The authors                                 |    |

| Become a published author                   |    |

| Comments welcome.                           |    |

| Commonic wolcome.                           |    |

| Chapter 1. Introduction                     | 1  |

| 1.1 Feature and function delivery schedules |    |

| 1.2 zSeries system                          | 2  |

| 1.3 New terminology                         | 4  |

| 1.4 z990 models                             | 5  |

| 1.5 Maximum channels                        | 5  |

| 1.6 Migration                               | 6  |

| 1.7 Statements of direction                 | 6  |

| 1.8 Limitations and considerations          | 7  |

|                                             |    |

| Chapter 2. Hardware details                 |    |

| 2.1 System frames                           |    |

| 2.2 Processors and MCMs                     |    |

| 2.3 Book package                            |    |

| 2.4 Memory                                  |    |

| 2.5 z990 models                             |    |

| 2.6 PU characterization                     |    |

| 2.7 I/O cages and adapters                  | 14 |

| 2.7.1 I/O adapters                          | 15 |

| 2.7.2 New I/O adapters                      |    |

| 2.7.3 I/O adapter configuration rules       |    |

| 2.8 I/O interfaces and identification       | 18 |

| 2.9 System control                          |    |

| 2.10 Power and cooling                      |    |

| 2.10.1 Cooling                              | 21 |

| 2.11 Concurrent changes                     | 22 |

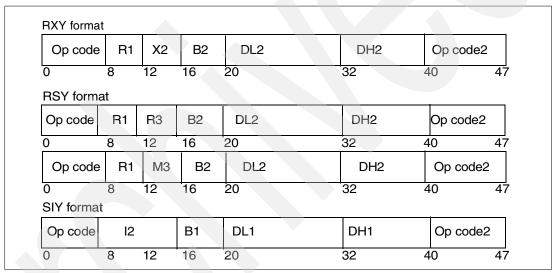

| 2.12 Instruction set                        | 22 |

| 2.13 Additional hardware elements           | 24 |

| 2.13.1 HSA                                  | 24 |

| 2.13.2 Internal battery feature             | 24 |

| 2.13.3 Support Elements                     | 25 |

| 2.13.4 Hardware Management Console          | 25 |

| 2.14 External time reference                | 25 |

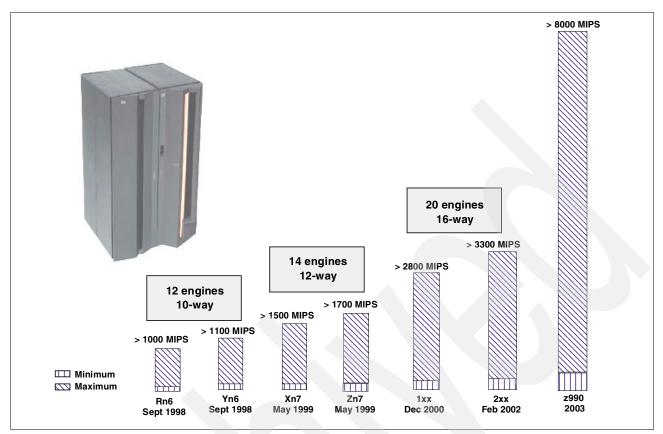

| 2.15 Basic zSeries comparisons              | 27 |

|                                             |    |

| Chapter 3. Discussion topics                |    |

| 3.1 Performance factors                     |    |

| 3.2 Channel subsystem                       |    |

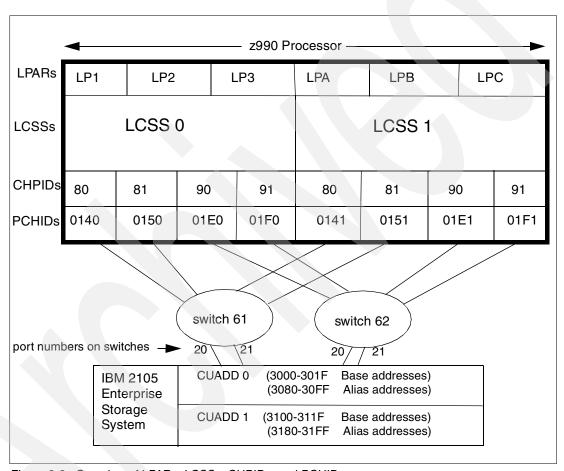

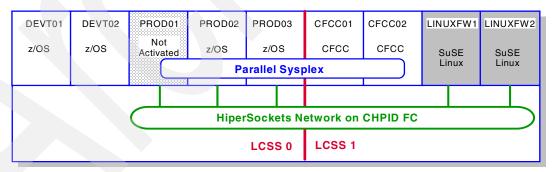

| 3.2.1 Logical Channel Subsystems (LCSSs)    | 32 |

| 3.2.2 IOCP example                          | 34 |

| 3.2.3 Spanned channels                      | 35 |

| 3.2.4 Channel definitions in the IOCP statement        |    |

|--------------------------------------------------------|----|

| 3.3 Cryptographic changes                              |    |

| 3.3.1 Initial cryptographic support                    |    |

| 3.3.2 Second phase support                             | 37 |

| 3.3.3 Functions not supported                          | 38 |

| 3.3.4 Functions changed and coexistence considerations | 38 |

| 3.4 Concurrent system upgrades                         | 38 |

| 3.5 New HMC/SE functions                               |    |

| 3.5.1 Integrated 3270 Console                          | 39 |

| 3.5.2 Integrated ASCII console                         | 40 |

| 3.5.3 Optional Strict password rules                   | 40 |

| 3.5.4 Customizable HMC Data Mirroring                  |    |

| 3.5.5 Extended console logging                         |    |

| 3.5.6 Operating System Messages display                |    |

| 3.6 SE and HMC connectivity                            |    |

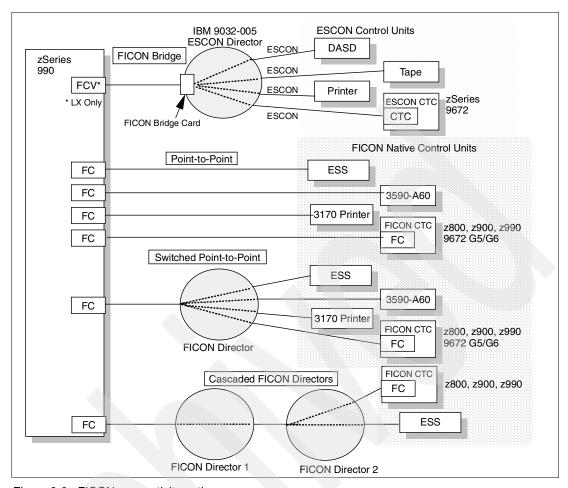

| 3.7 ESCON channels                                     |    |

| 3.7.1 Consideration for ES conversion channels         |    |

| 3.8 ESCON directors and multiple LCSSs                 |    |

| 3.9 HiperSockets                                       |    |

| 3.9.1 Defining HiperSockets in IOCP statements         |    |

| 3.9.2 Spanning HiperSockets over multiple LCSSs        |    |

| 3.9.3 Defining HiperSockets in the z/OS TCP/IP profile |    |

| 3.10 Channel measurement changes                       |    |

| 3.11 Sysplex coupling considerations                   |    |

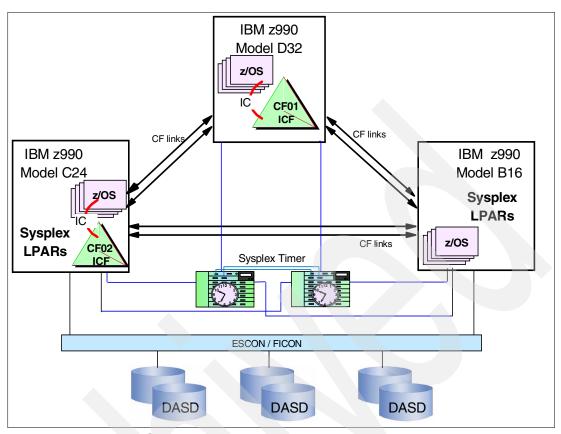

| 3.11.1 CF Links on z990                                |    |

| 3.11.2 CF considerations                               |    |

| 3.11.2 CF considerations                               |    |

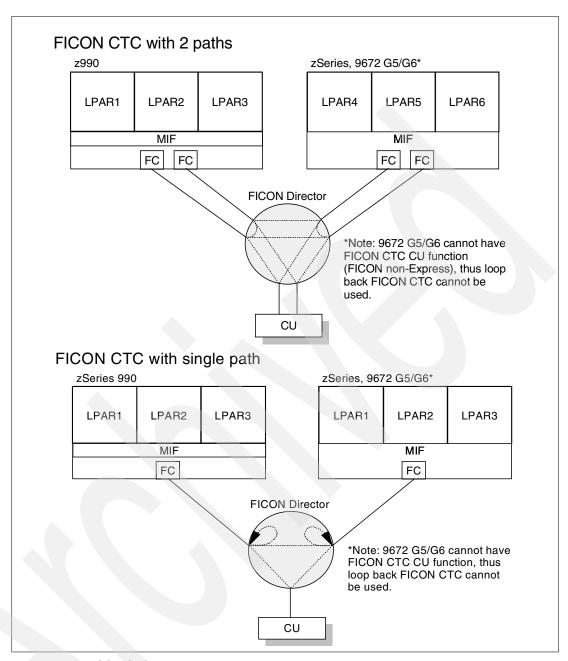

| 3.12.1 FICON CTC                                       |    |

|                                                        |    |

| 3.13 Characterization                                  |    |

| 3.13.1 Integrated Facility for Linux (IFLs)            |    |

| 3.13.2 Internal Coupling Facility (ICF)                |    |

| 3.13.3 Central Processor (CP)                          |    |

| 3.13.4 System Assist Processor (SAP)                   |    |

| 3.14 CHPID Mapping Tool overview                       |    |

| 3.14.1 Mapping function for the z990                   |    |

| 3.14.2 PCHID assignments                               |    |

| 3.14.3 CHPID Mapping Tool description                  |    |

| 3.14.4 Mapping Tool requirements                       |    |

| 3.14.5 Using the CHPID Mapping Tool                    |    |

| 3.15 RAS                                               |    |

| 3.16 LPARs                                             |    |

| 3.17 STIDP instruction changes                         |    |

| 3.18 OSA-Express adapters                              |    |

| 3.18.1 OSA-Express Fast Ethernet                       |    |

| 3.18.2 OSA-Express 1000BaseT Ethernet                  |    |

| 3.18.3 OSA-Express Gigabit Ethernet                    |    |

| 3.18.4 OSA-Express High Speed Token Ring               | 69 |

| 3.18.5 OSA-Express migration                           | 69 |

| 3.19 z/VM functions                                    |    |

| 3.20 Parallel channel planning                         | 70 |

| 3.20.1 Byte multiplexor                                | 71 |

| 3.20.2 Optica planning                                 |    |

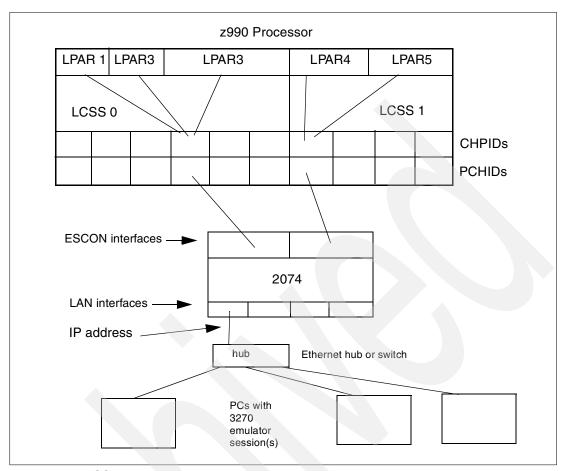

| 2.21 IPM 2074 utilization                              | 7/ |

| 3.22 Cable ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

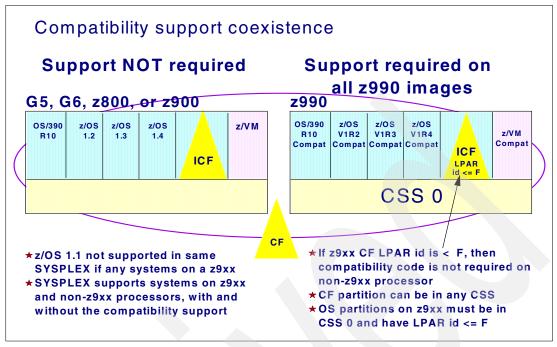

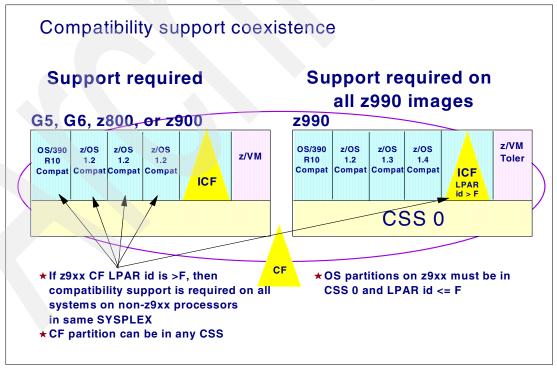

| Chapter 4. Software considerations  4.1 OS/390 and z/OS software considerations  4.1.1 Compatibility support and coexistence  4.1.2 Compatibility support restrictions  4.1.3 Exploitation support  4.1.4 Exploitation support considerations  4.2 z/VM software considerations  4.3 Linux software considerations  4.4 VSE/ESA™ software considerations                                                                                                                                                                                                | 79<br>80<br>85<br>85<br>85<br>89                     |

| Chapter 5. Migration considerations 5.1 Hardware migration considerations 5.1.1 ESCON channels 5.1.2 FICON channels 5.1.3 FICON CTC 5.1.4 Parallel channels 5.1.5 OSA-Express and OSA-2 adapters 5.1.6 ISC and ICB coupling links 5.1.7 HiperSockets 5.1.8 Cryptographic hardware 5.1.9 Memory                                                                                                                                                                                                                                                          | 91<br>92<br>92<br>93<br>93<br>94<br>94               |

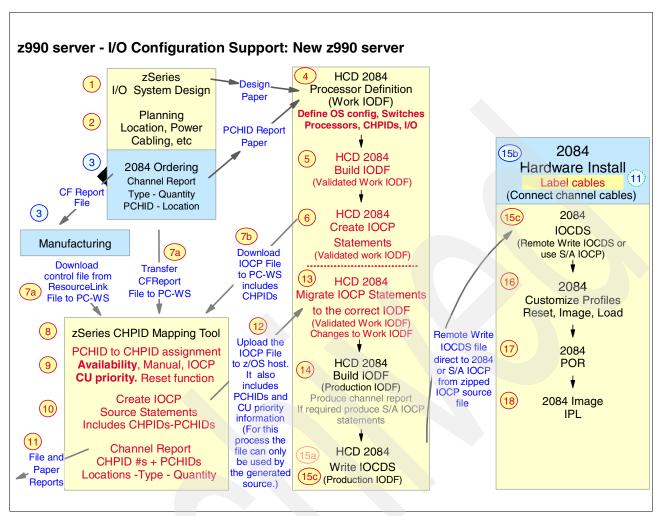

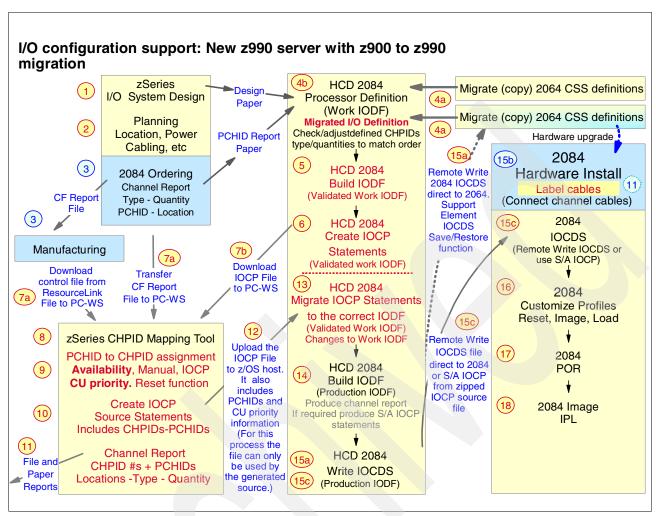

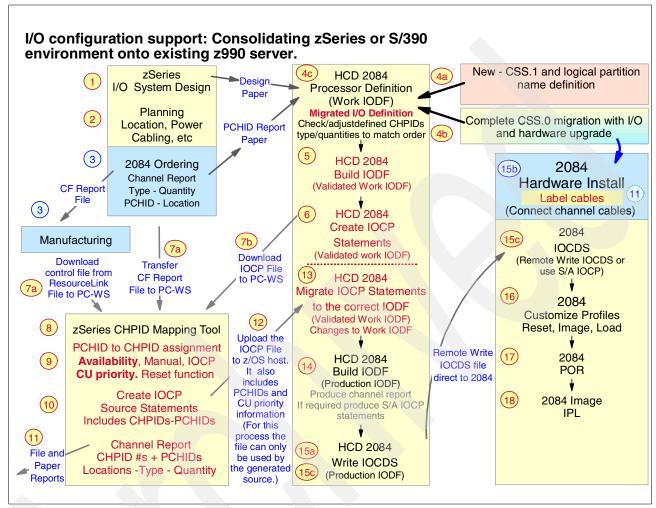

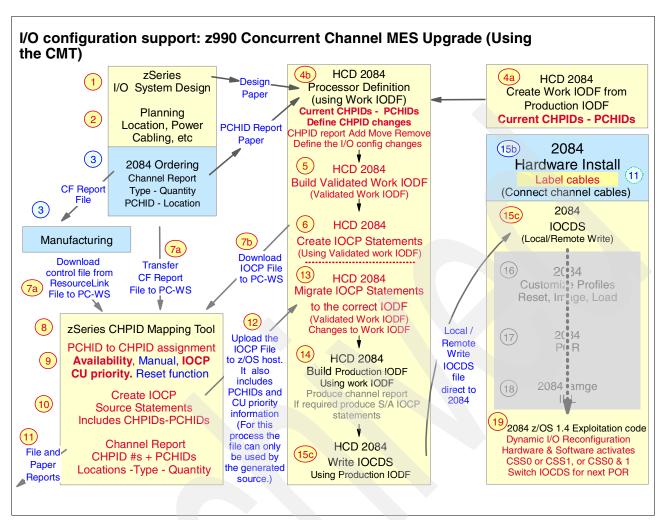

| 5.1.10 PR/SM. 5.1.11 Coupling Facilities. 5.1.12 Power, cooling, and floor space requirements. 5.2 OS/390 and z/OS software migration considerations. 5.2.1 PR/SM. 5.2.2 ISV software. 5.2.3 OS/390 and z/OS software support. 5.3 Migrating the I/O configuration definitions with HCD. 5.3.1 Defining a new z990 environment. 5.3.2 Upgrading an existing z900 to a z990 processor. 5.3.3 Consolidating a zSeries or S/390 environment onto an installed z990. 5.3.4 Upgrading an installed z990 with additional channels. 5.4 LPAR definition notes. | 95<br>96<br>97<br>97<br>97<br>98<br>99<br>103<br>107 |

| Chapter 6. Frequently asked questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 117                                                |

| Appendix A. New and changed instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 125                                                |

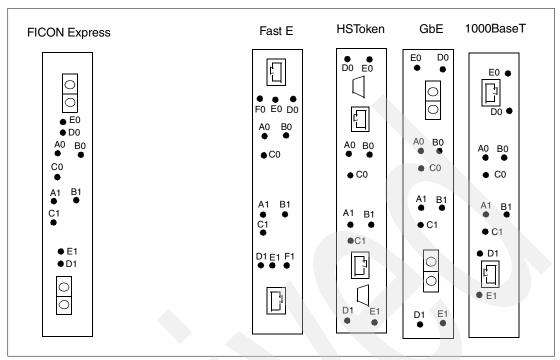

| Appendix B. I/O adapter indicator lights                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |

| Related publications  IBM Redbooks Other resources Referenced Web sites How to get IBM Redbooks IBM Redbooks collections.                                                                                                                                                                                                                                                                                                                                                                                                                               | . 133<br>. 133<br>. 133<br>. 133                     |

| Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 135                                                  |

# **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### COPYRIGHT LICENSE:

This information contains sample application programs in source language, which illustrates programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs. You may copy, modify, and distribute these sample programs in any form without payment to IBM for the purposes of developing, using, marketing, or distributing application programs conforming to IBM's application programming interfaces.

#### **Trademarks**

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

**@**server ™ OS/390® S/390® @server™ Parallel Sysplex® Sysplex Timer® **CICS®** PowerPC® VSE/ESA™ DirMaint™ PR/SM™ **VTAM®** Redbooks™ DB2® 3890™ **ESCON®** z/Architecture™ FICON™ Resource Link™ z/OSTM **IBM® RACF®** z/VM®  $MVS^{TM}$  $RMF^{TM}$ zSeries® S/370™ OS/2®

The following terms are trademarks of other companies:

ActionMedia, LANDesk, MMX, Pentium and ProShare are trademarks of Intel Corporation in the United States, other countries, or both.

Microsoft, Windows, Windows NT, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.

Java and all Java-based trademarks and logos are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

C-bus is a trademark of Corollary, Inc. in the United States, other countries, or both.

UNIX is a registered trademark of The Open Group in the United States and other countries.

SET, SET Secure Electronic Transaction, and the SET Logo are trademarks owned by SET Secure Electronic Transaction LLC.

Other company, product, and service names may be trademarks or service marks of others.

# **Preface**

The IBM® @server™ zSeries® 990 provides major extensions to existing zSeries architecture and capabilities. The concepts of books and channel subsystems are added to the architecture, and the maximum number of LPARs is increased. These architectural extensions provide the base for much larger zSeries machines. This IBM Redbook provides an overview of these changes, and goes into more detail in selected areas.

By removing memory, processor, and channel constraints, z990 can be used for major server consolidation activities. More granular options for nondisruptive maintenance, growth, and alterations provide better 7 x 24 x 365 operation. In general, no changes are needed for existing applications—allowing immediate growth into z990.

Readers are assumed to have a general understanding of existing S/390® and zSeries hardware. Terms, acronyms, abbreviations, and concepts associated with existing systems are used without further introduction.

#### The authors

**Bill Ogden** is a retired Senior Technical Staff Member at the International Technical Support Center, Poughkeepsie. Bill joined the ITSO (then the WTSC) in 1978 and has worked with a large number of S/360, S/370™, S/390, zSeries, and associated systems during these years.

**Luiz A Fadel** is a Senior Certified Consulting IT Specialist with IBM Brazil. He is responsible for zSeries pre-sales and z/OS technical support for Americas South Region (LA Countries). He is also responsible for supporting zSeries or z/OS ESPs and first installation, as well as critical situations in LA.

**Roger Fowler** is a Consulting IT Specialist with IBM United Kingdom Ltd. He is responsible for technical leadership of z/OS<sup>™</sup> and Parallel Sysplex® in EMEA Northern Region, and pre-sales zSeries technical support. He is also the IBM liaison officer for the Guide Share Europe Large Systems Group in the UK. Prior to joining IBM in 1988, Roger worked in large systems technical support for two large energy corporations and a financial institution.

#### **Extensive contributions**

The following people provided extensive help and expertise for this redbook.

**Bill White**, IBM Poughkeepsie, who helped us understand many of the details involved with recent I/O architecture, connectivity, and devices.

**Franck Injey**, on assignment from IBM France to the ITSO in Poughkeepsie, who helped with details about system setup and migration.

Parwez Hamid, IBM UK, who helped us understand the "big picture" (in detail!).

#### Additional help

We thank the following people for their contributions to this project:

**Joe Turner** and **Mike Scoba**, IBM Poughkeepsie, who helped organize this work.

Ken Trowell, recently retired from IBM Australia and now with IBM in Poughkeepsie.

**Dale Riedy,** IBM Poughkeepsie, who provided much information on z/OS compatibility and exploitation support.

# Become a published author

Join us for a two- to six-week residency program! Help write an IBM Redbook dealing with specific products or solutions, while getting hands-on experience with leading-edge technologies. You'll team with IBM technical professionals, Business Partners and/or customers.

Your efforts will help increase product acceptance and customer satisfaction. As a bonus, you'll develop a network of contacts in IBM development labs, and increase your productivity and marketability.

Find out more about the residency program, browse the residency index, and apply online at:

ibm.com/redbooks/residencies.html

#### **Comments welcome**

Your comments are important to us!

We want our Redbooks<sup>™</sup> to be as helpful as possible. Send us your comments about this or other Redbooks in one of the following ways:

▶ Use the online Contact us review redbook form found at:

ibm.com/redbooks

Send your comments in an Internet note to:

redbook@us.ibm.com

Mail your comments to:

IBM Corporation, International Technical Support Organization Dept. HYJ Mail Station P099 2455 South Road Poughkeepsie, NY 12601-5400

# 1

# Introduction

The original S/360 architecture has evolved in many ways since it was introduced in 1964. Two fundamental characteristics of this evolution have been:

Compatible evolution

IBM recognizes the total customer investment in data processing solutions and recognizes that application software (and the non-DP processes that are intertwined with these applications) represents the bulk of this investment. Therefore, the entire evolution of the system architecture has been planned with application compatibility in mind.

► Resolving constraints

Evolving hardware capabilities and evolving application designs produce various stress points in system designs. Over the years these stress points have included CPU performance, usable memory size, addressable memory size, I/O speed, I/O management overhead, I/O attachment capacity, and so forth. System architecture has evolved to relieve constraints in many areas.

#### Examples of this evolution include:

- ► Single processor systems evolved to multiple processor systems.

- Real memory systems evolved to virtual memory systems.

- Memory addressing (real and virtual) evolved from 24-bit to 31-bit to 64-bit addressing.

- ► I/O channels evolved from 16 channels to 256 channels.

- ▶ I/O addressing evolved from 3 hex digits (S/360) to 4 hex digits (XA architecture) providing up to approximately 64,000 addresses (device numbers) for I/O devices.

- A single operating system in the machine has evolved to LPARs providing up to 15 system images in one physical system.

- ► I/O management evolved from complex operating system functionality to System Assistance Processors (SAPs) that handle much of the work.

- ► I/O performance has evolved from parallel channels to ESCON® channels to FICON™ channels.

- ► Communication between similar systems has evolved from simple shared DASD to interconnected channels (CTCs) to Coupling Facilities and Parallel Sysplex.

- Advanced I/O interfaces have evolved from intricately programmed control units (such as the IBM 2701, 2702, 2703 products) to front-end processors (such as the IBM 3745) to OSA Express designs.

- ► I/O programming has evolved from the basic SIO-type instructions of the S/360 to the SSCH-related instructions and subsystem of the S/390, and to the QDIO model available with the z/Series.

- System monitoring and tracing has grown from simple sampling routines (high overhead), to hardware-assisted tracing instructions and to hardware-assisted channel and device usage measurements.

- ► Instructions for small program models (with strict 12-bit displacements) have been expanded through the *relative and immediate* instructions added to the architecture a few years ago. These instructions, intended primarily for compilers, provide more efficient instructions for larger program models.

The z990 provides another major evolutionary step. Key architectural limits of existing systems are addressed without significant impact to the application compatibility that is so important to IBM's customers. Among other elements, the z990 addresses:

- ► Total system processing speed. The largest z990 has several times the processing capacity of the largest z900 system.

- ► Total system memory. A z990 can have 8 GB to 256 GB memory.

- Total number of I/O channels. A z990 is architected to have more than 256 channels.

- Number of system images. A z990 is architected to have more than 15 LPARs.

- ▶ Additional channel and device measurements are available.

- Enhanced concurrent maintenance and upgrade capabilities.

- ▶ More efficient large program models, using long-displacement instructions.

- ► More efficient LAN operation, using larger data blocks and offloading more processing from the main processor to the I/O adapters.

Not all of these extensions are available in the initial release of the z990, but they are present in the *architecture* of the system. For example, two Logical Channel Subsystems are implemented in the z990, while the architecture implemented in the z990 allows more.

# 1.1 Feature and function delivery schedules

The z990 announcement includes functions and features that are available with initial system delivery, and additional functions and features that are planned to become available later. This redbook discusses all the functions that have been announced. Refer to the primary IBM announcement materials to understand which functions and features will be available initially and which will be available later.

The z990 announcement also included several IBM Statements of Direction (SODs) about possible future enhancements. These are briefly discussed in this redbook.

# 1.2 zSeries system

The z990 is a member of the zSeries family and uses the zArch architecture (formerly known as ESAME Architecture) and instruction set (with some extensions) that is used in the z900 and z990 machines. (The zArch Architecture is commonly known as "64-bit" architecture, although it provides much more than 64-bit capability.)

Completely new with the z990 is the concept of a *book* within a zSeries machine. The z990 offers four models: A08 (with one book), B16 (with two books), C24 (with three books), and D32 (with four books).

A book contains processors (PUs in normal zSeries terminology), memory, and connections to the I/O *cages*. A z990 has space for 1 to 4 books.<sup>1</sup> Each book has:

- ▶ 12 processor units.

- Within each book, a maximum of 8 processors may be used as CPUs. (Two are used as SAPs and two are reserved as spares.)

- 8 to 64 GB memory.

- ▶ Up to 12 connections to the I/O cages and/or ICB coupling channels.

While memory is resident in the book(s) it is used as a single SMP. All memory is addressable by any processor in any book. Stated another way, a given processor can address all the memory in the system and all the memory is coherent to programs.<sup>2</sup> L1 and L2 caches exist to improve performance, but they are not directly visible to programs. The memory structure is explored in more detail in "Memory" on page 12.

A z990 *book* might sometimes be labeled a *node*. IBM is not using the node terminology because it creates an incorrect impression. The term node is often used for an independent processor, or, in a sense, a loosely-coupled processor. This is not the case for the z990. All processors and memory, on all books, are part of a single symmetric multiprocessor (SMP) system.

The processors (normally known as Processor Units or PUs) are new. There are one or two processors on a chip ("single core" or "dual core" design), and each of the processors has the duplicate I and E units that are used for internal checking in all zSeries machines. Processor cycle time is .83 ns.<sup>3</sup> A fixed mixture of single and dual core chips is used in every system and, their positions are fixed by the design of the underlying ceramic carrier. Each processor provides superscalar operation, meaning that multiple instructions may begin execution in a cycle and some elements of an instruction may be executed out of sequential order.

z900 machines can have multiple instructions in process during a single cycle, while the z990 can have multiple instructions start and/or complete during a single cycle. Instruction completion is always in the order of the original instructions, but the z990 can perform memory accesses (required by an instruction) out of order. The net effect is improved performance. The degree of improved performance depends somewhat on the nature of the workload. The processor is discussed in more detail in "Processors and MCMs" on page 10. Performance considerations are discussed in "Performance factors" on page 29.

All z990 systems have two frames. These appear roughly the same as a two-frame z900 system and have the same frame names (A and Z frames). Some, but not all, I/O cards from a z900 can be used in a z990 system. The I/O cards are placed in I/O cages (Cargo cages<sup>4</sup>) that are similar to those in a z900. The A frame contains the processor/memory books and one I/O cage. The Z frame contains 0, 1 or 2 I/O cages and two ThinkPads® that are used as Support Elements.

The frames contain extensive power supplies, system controls, and a new hybrid cooling system. A more extensive description of the frames appears in "Power and cooling" on page 21.

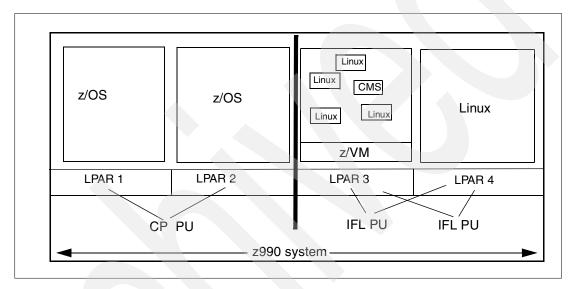

z990 systems run only in *LPAR mode*, and there is no *basic mode*. Up to 30 LPARs may be defined. There are new rules associated with LPAR<sup>5</sup> definitions and a new type of

<sup>&</sup>lt;sup>1</sup> Again, we stress that not all elements are available for initial z990 shipments. For example, only two books may be ordered for initial shipments.

<sup>&</sup>lt;sup>2</sup> There may be minor exceptions to this statement for certain privileged state-changing instructions.

<sup>&</sup>lt;sup>3</sup> This equates to a 1.2 GHz clock rate. However, we avoid this terminology because it leads to completely incorrect comparisons with clock rates in other architectures (in the same way that zSeries MIPS often are compared incorrectly with various metrics in other architectures).

<sup>&</sup>lt;sup>4</sup> The IBM development name for these I/O cages was *Cargo*, and this name is still informally used.

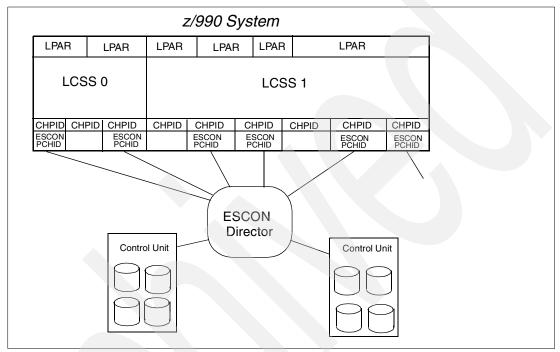

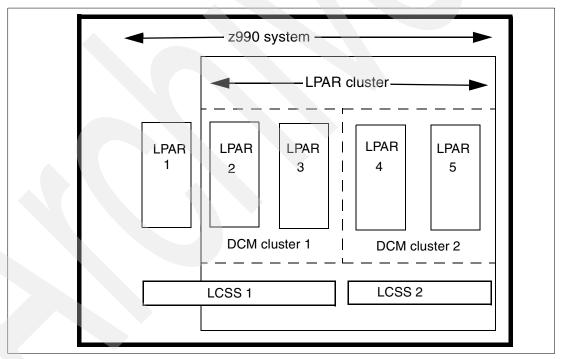

definition—for Logical Channel Subsystems (LCSSs)—is required. This is discussed in more detail in "Channel subsystem" on page 32 and throughout this redbook. Briefly, the key rules include:

- Every LPAR must be associated with a Logical Channel Subsystem. Multiple LPARs (up to 15) can be associated with a single Logical Channel Subsystem.

- A Logical Channel Subsystem can define and use a maximum of 256 channels (CHPIDs).

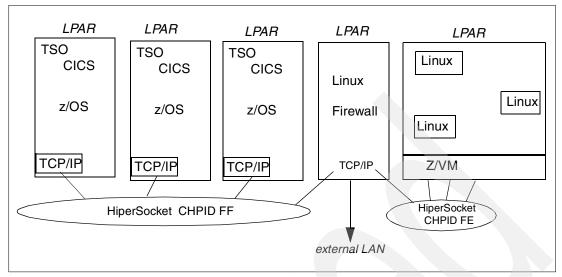

- ► Some channel types, such as ESCON, can be associated with only a single Logical Channel Subsystem. Other channel types, such as HiperSockets, can be associated with multiple Logical Channel Subsystems.

- ► Logical Channel Subsystem definitions are part of the overall IOCDS definition. These definitions may be done through HCD or through direct IOCP statements in the operating system, Support Element or HMC.

# 1.3 New terminology

A number of new terms are associated with the z990 machines. Important new terms (and concepts) include:

▶ Books

A book contains processors, memory, and connections to I/O cages. A z990 can have one to four books.

► Logical Channel Subsystems (LCSSs)

A LCSS contains up to 256 CHPIDs. An LPAR (or several LPARs) is associated with a single LCSS. An LPAR (and the operating system running in it) sees a maximum of 256 CHPIDS, and all the I/O control functions are compatible with earlier systems which had a maximum of 256 CHPIDs.

**Note**: LCSSs are not an optional feature; the capability and *requirement* of using LCSSs is inherent in z990 systems.<sup>6</sup>

► A Physical Channel ID (PCHID)

This reflects the physical identity of a channel-type interface and has a range of X'000' through X'6FF'. A PCHID number is based on the I/O cage number, the adapter slot number, and the connector number of the I/O adapter. A unique PCHID exists for every potential channel interface connector in the system. See "I/O interfaces and identification" on page 18 for a table of PCHID numbers.

A CSS.CHPID is assigned to a PCHID. The traditional CHPID numbers are limited to one byte or 2 hexadecimal digits. They are in the range 0 - 255. As announced, a z990 system may have up to two Logical Channel Subsystems. A Logical Channel Subsystem (LCSS) can have a maximum of 256 CHPIDs.

New mapping specifications (in an IOCDS) are used to map PCHIDs to CHPIDs within an LCSS. A notation such as 1.C1 = 23F means CHPID C1 in LCSS 1 is assigned to PCHID 23E. PCHID 23E is connector 14 in the adapter in slot 22 in I/O cage 1. This is covered in more detail in "Channel subsystem" on page 32.

- System-used and customer-used PUs:

- System-used PUs are used for basic SAPs or spares.

<sup>&</sup>lt;sup>5</sup> Strictly speaking, "LPAR" is the name of a system mode that uses logical partitions (LPs). However, the use of "LPAR" to indicate a logical partition is so widespread that we continue such usage in this redbook.

<sup>&</sup>lt;sup>6</sup> HCD and IOCP definitions will default to LCSS 0 if an LCSS is not specified, so it is possible to create a working IOCDS without LCSS parameters in HCD or IOCP source statements.

<sup>&</sup>lt;sup>7</sup> Not all this range is used.

- Customer-used PUs may be used as CPUs, ILFs, ICFs, or additional SAPs.

- A customer may purchase a CP or IFL and leave it unassigned. This might be done for software cost control purposes. A later IBM MES action is needed to enable the PU.

- Otherwise unassigned PUs are use for sparing after the reserved spare PUs are used.

Do not confuse the hardware I/O subsystem with Logical Channel Subsystem. A z990, regardless of the number of books or PUs installed, has only one hardware I/O channel subsystem. However, it can have multiple Logical Channel Subsystems (LCSSs). The multiple Logical Channel Subsystems permit the system (typically via multiple operating systems in multiple LPARs) to address and use more than 256 channels (CHPIDs).

#### 1.4 z990 models

The z990 is offered in four models, although only the first two models listed here are available for initial shipments. The model is directly related to the number of books included in the system. The number of processor units purchased for each book is selected by feature codes and is not reflected in the system model number. The models are:

- ► IBM 2084-A08 (One book, with up to 12 processors, 12 STI connectors, with a maximum of 8 customer-used PUs and a maximum of 64 GB memory)

- ► IBM 2084-B16 (Two books, with up to 24 processors, 24 STI connectors, with a maximum of 16 customer-used PUs and a maximum of 128 GB memory)

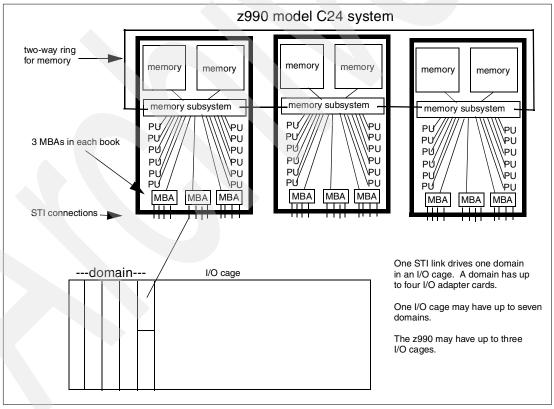

- ► IBM 2084-C24 (Three books, with up to 36 processors, 36 STI connectors, with a maximum of 24 customer-used PUs and a maximum of 192 MB memory)

- ► IBM 2084-D32 (Four books, with up to 48 processors, 48 STI connectors, with a maximum of 32 customer-used PUs and a maximum of 256 GB memory)

As can be seen, the A, B, C, or D in the model number indicates 1, 2, 3, or 4 books. The number after the A, B, C, or D indicates the *maximum* number of zSeries CPs/IFLs/ICFs that can be ordered and enabled. (Remember that additional processors are included for SAPs and spares.)

Note that the system model number no longer reflects the number of processors that are enabled for use. It reflects only the maximum number of customer-used processors that could be enabled (if purchased). The model number also reflects the number of books installed.

## 1.5 Maximum channels

The maximum number of channels for a z990 depends on a number of factors:

- ► The maximum number of *usable* CHPIDs is 256 x LCSSs; that is, 256 (the maximum number of CHPIDS that can be addressed by a Logical Channel Subsystem) times the number of Logical Channel Subsystems used. The z990 announcement provides for two Logical Channel Subsystems, allowing up to 512 CHPIDS to be used.<sup>8</sup>

- ► The number of STI connections available for I/O cages. A z990 model A08, for example, has 12 STI connections available and this limits the number of I/O slots that can be used.

- ► The number of I/O adapter slots available. There are three I/O cages, each containing 28 slots for I/O adapters.

<sup>&</sup>lt;sup>8</sup> This number is reduced if spanned channels are used. Also, remember that a single z/OS image supports a maximum of 256 channels.

- ► The number of channels on various I/O adapters. For example, an ESCON adapter can provide up to 15 usable channels, while a FICON adapter provides two channels.

- ► Maximum limitations for various I/O adapters. For example, a maximum of 60 FICON adapters (providing 120 channels) can be installed.<sup>9</sup>

It is possible to install more physical channels than can be used at any one time. Channel adapters are discussed in more detail in "I/O cages and adapters" on page 14.

# 1.6 Migration

The z990 introduces significant new architectural changes. Software exploitation of these changes is expected to be introduced in phases. A migration from an existing zSeries system to a z990, based on the software available with initial z990 shipments, should be relatively simple.

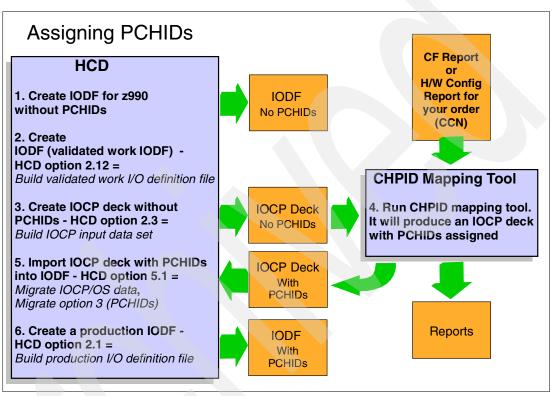

z/OS functions available with initial z990 shipments use only a single Logical Channel Subsystem. This provides an environment very similar to that of current zSeries machines. The most significant migration activity at this level might be an IOCP (or HCD equivalent) move. A z990 contains more information in an IOCP. A CHPID Mapping Tool is available and should ease this migration. The new PCHID addressing level can be used to make the CHPID numbers for the z990 generally match the CHPID numbers in an existing zSeries machine. This can considerably reduce the effort in migrating a complex IOCDS.

These aspects of migration are discussed in more detail in "Migrating the I/O configuration definitions with HCD" on page 98.

## 1.7 Statements of direction

IBM included a number of Statements of Direction (SODs) with the z990 announcement. Refer to the formal announcement material for the complete list and exact formulation of these statements. In this section we briefly mention several of the SODs.

- ▶ IBM intends to support four Logical Channel Subsystems on the z990.

- The announced support is for two LCSSs. This redbook discusses multiple Logical Channel Subsystems in general, although specific examples use only two LCSSs. The maximum number of channels supported on a single z/OS image will be 256.

- IBM intends to support up to 60 LPARs on the z990.

- The announced support is limited to 30 LPARs.

- ► IBM intends to support greater than 16 engines in a single image on appropriate releases of z/OS and z/VM® on the z990.

- ▶ IBM intends to support an optional Smart Card Reader, attached to a TKE workstation, permitting secure storage, convenient transport, and rapid re-entry of key parts for the z990.

- The PCIXCC adapter is planned to be available later.

- ► IBM intends to provide z/VM guest support of the PCIX Cryptographic Coprocessor (PCIXCC) adapter.

Except for a few tables listing maximum values (which correspond to the announced z990) the discussions in this redbook should be compatible with these statements of direction.

<sup>&</sup>lt;sup>9</sup> The number of OSA-Express adapters installed and other factors can reduce this number.

#### 1.8 Limitations and considerations

There are several key z990 considerations when migrating from earlier systems. These include:

- ▶ Parallel ("bus and tag") channels are not supported. Converters (which connect an ESCON channel to a parallel control unit) are supported. The details are the same as for the z800 systems. IBM 9034 converters (commonly known as *Pacer* boxes) may be used, as well as converters from Optica Technologies, Incorporated. See "Parallel channel planning" on page 70 for more details.

- ► Hardware cryptographic functions are different:

- The CMOS cryptographic coprocessors are not available.

- The PCICC cryptographic adapters are not available.

- The PCICA cryptographic adapter is available.

- New cryptographic-assist instructions are included in every processor unit.

- A new PCIX Cryptographic Coprocessor (PCIXCC) adapter will be available October 31, 2003.

More details about the cryptographic changes can be found in "Sysplex coupling considerations" on page 49.

- ▶ Older channel and communications adapters cannot be used. These include:

- FICON adapters; FICON Express adapters are used instead.

- OSA2 adapters; OSE-Express adapters are used instead.

- · There is no replacement for FDDI adapters.

- ATM adapters (which are OSA-Express adapters). Customers using ATM functions should consider using ATM interfaces in outboard switches and routers.

- Existing OSA-Express Fast Ethernet adapters on z900 systems can be moved to a z990, but new orders must be for the new 1000BaseT Ethernet adapter.

- ► A z990 IOCDS must contain PCHID numbers that assign CHPIDs to specific hardware channels. These assignments must be added to existing HCD (and IOCP) definitions.

- ▶ The z/OS versions available with initial z990 shipments can use only the first LCSS.

- ▶ If appropriate, you must use a new IOCP program that includes support for z990 functions.

# Hardware details

This chapter provides an overview of the z990 hardware, with some comparisons to earlier systems. Many of the features, functions, and considerations briefly described here are further discussed in "Discussion topics" on page 29.

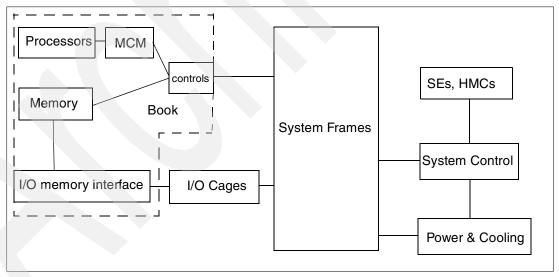

A simplified view of the building blocks of a z990 system is shown in Figure 2-1. This figure is not intended to depict the operation of a z990 system. It simply lists the general elements discussed in this chapter and roughly indicates how they are related to each other.

Figure 2-1 Organization of descriptions in this chapter

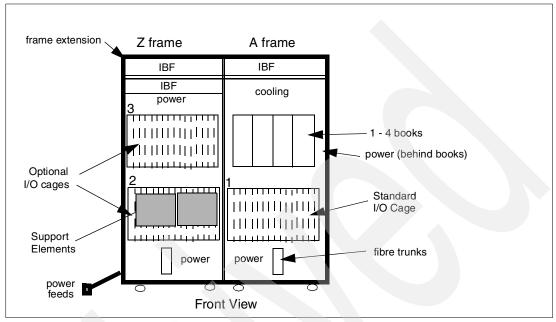

# 2.1 System frames

All z990 systems have two frames. The general content of the frames is shown in Figure 2-2 on page 10. The actual design (especially for power and cooling components) is much more complex than indicated, of course, but this diagram serves as a starting point.

The Z frame is always present, even if no I/O cages are installed in it. It will always have the two ThinkPads used as Support Elements and basic power components. The ThinkPads are mounted somewhat differently than on z900 or z800 machines, but they fold out for use in the same general manner as with a z900 machine.

Figure 2-2 General frame arrangement

The minimum system is a model A08 (which has one book). The books contain the processors and memory of the system.

The basic frames are 40 EIU units high, with a breakpoint at 38 EIUs. I/O cage 1 is in the bottom of the A frame. I/O cage 2 is in the bottom of the Z frame, and I/O cage 3 is in the top of the Z frame.

The approximate dimensions are:

- ▶ 158 cm deep (62 inches), including the covers

- ▶ 194 cm high (76 inches), including the casters

- ▶ 154 cm wide (61 inches), both frames together

- ▶ 705 kg (1550 pounds) for the A frame (without the internal battery feature)

- ▶ 790 kg (1738 pounds) for the A frame (with the internal battery feature)

- ► 682 kg (1500 pounds) for the Z frame (without the internal battery feature)

- ► 767 kg (1688 pounds) for the Z frame (with the internal battery feature)

These weights assume a full load of I/O adapters, but do not include the covers. The weights may change slightly depending on the exact mixture of I/O cards used. The top sections (used for the battery feature) can be removed, if necessary, to move the system through a smaller opening.

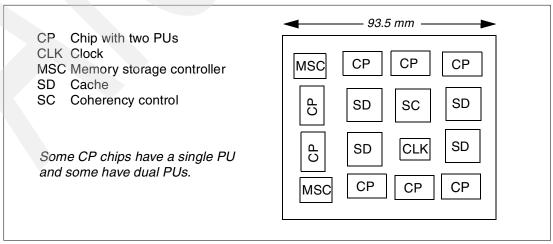

### 2.2 Processors and MCMs

There are eight customer-available PUs on each MCM. Each resides on a separate processor chip, using all of the eight processor chip sites available. In addition, two SAP and two spare PUs are needed. These are implemented with *dual core* chips containing two complete PUs. Each PU has dual instruction and execution units (I and E units) that are used

to verify internal operation. These additional I/E units, used for internal checking within a PU, are not further mentioned in this discussion. Do not confuse them with the two full-function PUs that are on a dual-core processor chip.

The processors have a superscalar design, meaning that several instructions may be processed, started, and/or ended at once and that some processing steps within an instruction may be out of sequential order. Each processor (and there are 12 per book, in a mixture of single-core and dual-core chips) can decode up to 3 instructions per cycle and complete up to 3 instructions per cycle. Some instructions complete in a single cycle, while others involve a pipeline of internal steps. Storage accesses may be out of sequential order, but instruction completion is in sequential order. (In these comments, *sequential order* means the order in which the instructions appear to be issued by the program.)

Each processor has a dual L1 cache, meaning that separate caches exist for instructions and data. Both I and D caches are 256 KB. Both the I and D caches have their own Translation Lookaside Buffer (TLB) with 512 entries. In addition, there is a new second-level TLB with 4096 entries. There is also a Branch History Table (BHT) with 8 K entries. All of these caches, TLBs, and BHT are four-way associative.

An L2 cache exists in each book and is 32 MB. The L2 caches of all books are connected through a ring structure, and it is the L2 cache operation that provides the unified, coherent memory seen by all books.

Floating point operation has been redesigned to enhance Binary Floating Point (BFP) performance, bringing it to at least the same level as traditional Hexadecimal Floating Point (HFP) performance.

New functions have been added to assist cryptographic operations. These are new (synchronous) instructions for several symmetric (clear key) cryptographic operations. Every PU has these new functions. (The separate cryptographic coprocessors that were associated with a small number of PUs in earlier systems no longer exist.)

The processor chips are mounted on a Multiple Chip Module (MCM), along with a number of other chips required at this level, as roughly illustrated in Figure 2-3. MCMs are the building blocks for all recent S/390 and zSeries machines. The MCM itself is glass-ceramic with many internal layers of connections. The z990 MCM is 93x93 mm (smaller than the z900 MCM) and is built without internal thin-film layers. (This provides simpler and more robust construction.)

Figure 2-3 General MCM layout

The chip notation in the figure is sometimes written as SCD (instead of SD) for cache chips and SCE (instead of SC) for coherence and control chips. Also remember that some processor chips have two PUs on them. There are a total of 12 PUs on the MCM, of which a maximum of 8 can be ordered for customer use as CPs. IFLs. or ICFs.

The user cannot select specific PUs as spares, SAPs, or CP/IFL/ICFs, or disabled. This selection is made by the system control code and can change due to configuration changes or sparing actions.

The memory interface chips (MBAs) are not on the MCM, but on separate riser cards in the book. This is a design difference from z900 machines, where the MBAs were on the MCM.

# 2.3 Book package

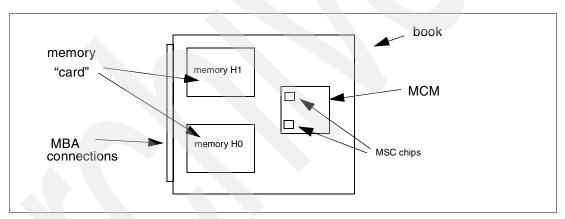

Books are sometimes described as *cards*, but a book physically appears as a box. A book plugs into one of four slots in the processor cage of the z990. A model A08 system has at least one book and a model D32 has four books. One or two memory "cards", the MCM, and various other chips and connectors are mounted in each book. A conceptual view of a book is shown in Figure 2-4. A book is fairly large, about 56 cm high and 14 cm wide (about 22 inches high and 5.5 inches wide) and weighs about 32 kg (70 pounds) with both memory cards fully populated.

Figure 2-4 Physical book layout (with the external "box" cover removed)

The book is physically large for several reasons. The size makes cooling easier. It also matches the size and connectors on several power supplies that are placed in the back of the same frame cage that holds the books. (The books are in the front of this cage.)

# 2.4 Memory

A z990 book contains an MCM (with processors) and two memory cards. These cards also might more accurately be described as *boxes*. They are enclosed units containing DIMMs (strips with memory chips). A memory card is removable as a unit. Each card physically contains 8, 16, or 32 GB of memory<sup>1</sup>. Two cards are always present for every book and must have the same amount of memory. Two 32 GB cards provide 64 GB, which is the maximum memory for a book.

These numbers are the amount of usable memory. Considerably more memory is actually present and is used for checking, redundancy, and sparing purposes.

Different books may have different memory sizes. The system memory is the total of the book memories. A book may have more memory installed than is enabled. IBM LICCC<sup>2</sup> specifications determine how much memory is available for use. Customers may order memory in increments of 8 GB per book. IBM controls the distribution of purchased memory across the system books.

Each card provides two memory ports. Each port can process four *fetch* and four *store* operations concurrently. Each access operation provides 128 bits (16 bytes) of usable data. (The storage path is actually 140 bits wide and includes a sophisticated sparing function.) While theoretical rates are higher, a practical workload may transfer up to about 7 GB/second for each port, thus providing up to approximately 28 GB/second for memory access in a book.

Spare memory chips are not used for main memory. Spare memory elements, used automatically as needed, are present in a distributed fashion. A description of the sophisticated sparing process is beyond the scope of this redbook.

Separate circuitry is used for storage protect keys and provides triple redundancy with a voting mechanism in case of errors. An additional spare set of memory for storage protect keys is present and is used to replace a failing set. System control circuitry keeps track of protect key memory errors and decides when to switch to the spare memory set.

Figure 2-5 provides a high-level conceptual illustration of the memory connectivity structure.

Figure 2-5 Overview of memory access for the z990 with three books

<sup>&</sup>lt;sup>2</sup> IBM Licensed Internal Code Controlled Configuration.

#### 2.5 z990 models

A z990 system has one to four books. Each book has 0 - 8 customer-used PUs, although a book with no customer-configured PUs would be unusual. (The system must have at least one configured CP, IFL, or ICF.) Each book has 8 - 32 GB memory, and each book has 12 STI connections. These interfaces are the links to external I/O devices and to specialized adapters.

Figure 2-5 on page 13 illustrates a model C32 system with three books. Note the *ring* that connects the memory subsystems of the three books together. This is a key element of the z990. It is actually two rings, one running clockwise and one running counterclockwise. Both loops are normally used as closed loops for maximum bandwidth and minimum latency; if necessary, they can run in open modes with reduced performance. This memory subsystem provides the L2 cache.

The memory ring is used to cause the memory in all the books to function as a single memory system. For example, if each book in the system shown in Figure 2-5 contains 32 GB, then the total system functions with a single 96 GB memory. The memory subsystem coordinates cache, STI accesses, memory ring functions, and local memory access such that the total system memory appears as a single coherent memory. Any PU or I/O connection in any book can access memory anywhere in the system. Software does not see memory as separated into books.

Different books can contain different amounts of memory. The system memory is the total of the books' memory.

Two oscillator cards (for redundancy) and two External Time Reference (ETR) cards (for redundancy) are shared by all books. ETR functions are discussed in "External time reference" on page 25.

# 2.6 PU characterization

PUs are ordered in single increments. A system must have one PU enabled as a CP, IFL, or ICF. Otherwise, the number of PUs ordered is not tied to the z990 model that is ordered. You could, for example, order a model D32 (four books with a maximum of 32 PUs enabled as CP/IFL/ICFs) and order only a single CP.

PUs are *characterized*. That is, they are assigned to be a CP, an IFL, an ICF, or an additional SAP. (There are also options to order unassigned PUs. This is discussed in "Concurrent system upgrades" on page 38.) You can place an order (an MES order) for IBM to change the characterization of your PUs.

# 2.7 I/O cages and adapters

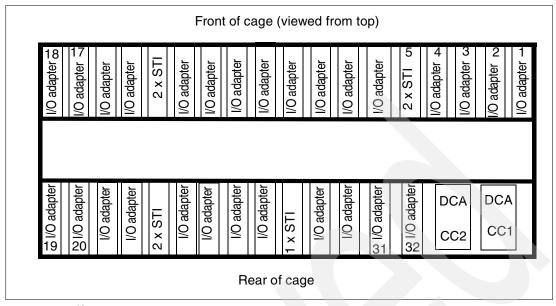

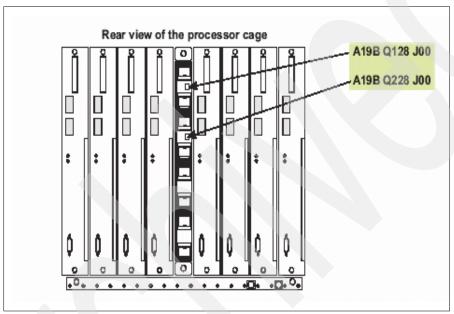

The I/O cages are the same as used with z900 machines, except that the DCAs (power supplies and cage controllers) and STI cards are new. A cage is roughly outlined in Figure 2-6 on page 15.

Figure 2-6 I/O cage

Notice that slots 5, 14, 23, and 28 are used for STI connections. There are two such connections in slots 5, 14, and 23, while slot 28 has a single STI connection. (The "other half" of slot 28 may be used for a power sequence control (PSC) card.) IBM selects which slots are used for I/O adapters and supplies an appropriate number of cages and STI cables. An STI cable goes directly from an I/O cage to an STI connector on a book. Each STI connection controls a *domain* of four I/O slots.

The assignment of slots to domains for each I/O cage is as follows:

| Domain | I/O Slots in domain |

|--------|---------------------|

| 0      | 1, 3, 6, 8          |

| 1      | 2, 4, 7, 9          |

| 2      | 10, 12, 15, 17      |

| 3      | 11, 13, 16, 18      |

| 4      | 19, 21, 24, 26      |

| 5      | 20, 22, 25, 27      |

| 6      | 29, 30, 31, 32      |

|        |                     |

## 2.7.1 I/O adapters

The I/O adapters initially available for the z990 are a subset of the adapters used with the z900, plus one new adapter. The subset excludes parallel channel, FDDI, ATM, and OSA-2 adapters. The various adapters that may be used are discussed at greater length in Chapter 4, "Software considerations" on page 79. Table 2-1 provides a brief summary:

Table 2-1 Summary of I/O adapters

| Description      | I/O Cage<br>slot? | Increment<br>(ports) | Ports per card | Maximum cards | Max ports<br>(CHPIDs) | Notes   |

|------------------|-------------------|----------------------|----------------|---------------|-----------------------|---------|

| ESCON channels   | Yes               | 4                    | 15 max         | 69            | 1024                  | 1       |

| FICON Express    | Yes               | 2                    | 2              | 60            | 120                   | 2, 6    |

| Fast Ethernet    | Yes               | 2                    | 2              | 12            | 24                    | 3, 4, 6 |

| Gigabit Ethernet | Yes               | 2                    | 2              | 24            | 48                    | 3, 6    |

| Description           | I/O Cage<br>slot? | Increment<br>(ports) | Ports per card | Maximum cards | Max ports<br>(CHPIDs) | Notes |

|-----------------------|-------------------|----------------------|----------------|---------------|-----------------------|-------|

| High Speed token ring | Yes               | 2                    | 2              | 24            | 48                    | 3, 6  |

| 1000BaseT Ethernet    | Yes               | 2                    | 2              | 24            | 48                    | 3, 6  |

| PCICA crypto          | Yes               | 2 engines            | 0              | 6             |                       |       |

| PCIXCC crypto         | Yes               | 1 engine             | 0              | 4             |                       |       |

| ICB-4 (CF link)       | No                | 1                    |                |               | 16 links              | 5     |

| ICB-3 (CF link)       | Yes               | 1 link               | 2              | 8             | 16 links              | 5     |

| ICB (ICB-2) (CF link) | Yes               | 1 link               | 2              | 4             | 8 links               | 5     |

| ISC-3 (CF link)       | Yes               | 1 link               | 4              | 8             | 32                    | 5     |

| HiperSockets          | No                |                      |                |               | 16                    |       |

| IC channel (CF link)  | No                |                      |                |               | 32                    |       |

- Note 1. Remember that a maximum of 512 channels are available initially.

- Note 2. FICON Express adapters are also used for FCP channels.

- Note 3. The total number of OSA Express cards is limited to 24.

- Note 4. Existing OSA-Express Fast Ethernet adapters on z900 systems may be carried forward, but new adapters cannot be ordered.

- Note 5. A maximum of 32 external CF links plus 32 internal CF links may exist.

- Note 6. The total number of FICON Express Adapters plus OSA-Express adapters plus

- PCICA/PCIXCC cards is limited to 20 in a single I/O cage.

The maximums listed in this table assume that sufficient I/O cages and books (to provide STI connection) are installed.

# 2.7.2 New I/O adapters

The OSA-Express 1000BaseT Ethernet Adapter is new and replaces the OSA-Express Fast Ethernet adapter. (As noted, existing OSA-Express Fast Ethernet Adapters may be carried forward from z900 systems, but new ones cannot be ordered.) The new adapter uses copper connections and offers 1000 Mbps, as well as 100 Mpbs and 10 Mpbs, operation. This means that two gigabit Ethernet adapters are available:

- ► The OSA-Express Gigabit Ethernet Adapter uses fiber connections.

- The OSA-Express 1000BaseT Ethernet Adapter uses copper connections.

As with other OSA-Express adapters, two ports (channels or CHPIDs) are installed in each adapter and are used independently.

A new OSA-Express Gigabit Ethernet adapter is available and provides new fiber connectors. Both new adapters (1000BaseT and Gb) provide a checksum offload function that will be supported by z/OS 1.5 for use with IPv4 (but not IPv6). This function reduces CPU overhead during IP transfers.

The PCIXCC adapter (cryptographic adapter) is new and requires an I/O slot for each adapter.

# 2.7.3 I/O adapter configuration rules

The following general rules apply for z990 systems:

- ► A maximum of three I/O cages, with 28 adapter slots per cage, may be used. Each domain (4 slots) within an I/O card requires an STI connection.

- ► OSA-Express cards include:

- High Speed token ring (HSTR)

- Gigabit Ethernet (GbE)

- Fast Ethernet (FE) for adapters carried forward from a z900 system

- 1000BaseT Ethernet, which replaces the OSA Express Fast Ethernet adapter

- OSA-Express features are ordered in increments of two ports (equal to one adapter card)

There is maximum of 24 OSA-Express cards per system.

- ► For FICON Express, OSA-Express, PCICA, and PCIXCC cards, taken together, the maximum is 20 of these cards per I/O cage.

- ► There is a maximum of 60 FICON Express cards (120 channels) per system, less any restrictions imposed by the number of OSA-Express, PCICA, and PCIXCC cards installed.

- ► There is a maximum of 6 PCICA cards per system and 2 per I/O cage.

- ► There is a maximum of 4 PCIXCC cards per system and 2 per I/O cage.

- ► ESCON adapters

- Only the 16-port ESCON adapters may be used.

- The first ESCON channel(s) require two adapters.

- After the first two adapters, single adapters are added.

- ESCON channels are ordered in increments of 4.

- IBM will determine the number of adapters needed, based on the number of ESCON channels ordered. All the potential channels on an adapter might not be enabled, depending on the total number of channels ordered.

- A maximum of 15 of the 16 ports on an adapter will be enabled. The 16th port is a spare.

#### ► ICB links

- ICB-4 links are for a z990-to-z990 connection and operate at 2.0 GB/second. These

links use direct connections to a book and have no connections to I/O cages. There

maximum number of links is 16 per system, but may be further limited by the number of

free STI connections on the installed books. A special cable is needed for ICB-4

connections.

- ICB-3 links are for connections to zSeries machines and operate at 1 GB/second. An STI-3 adapter card is used in an I/O cage, and this provides two ICB-3 ports. There is a maximum of 8 STI-3 cards (providing 16 ICB-3 links) per system.

- ICB (also known as ICB-2) links are for connections to IBM 9672 G5/G6 machines (and can be used for connections to other zSeries machines) and operate at 333 MB/second. The STI-2 adapter card plugs into an I/O cage and provides two ICB-2 ports. A maximum of 4 adapter cards (providing 8 links) may be ordered.

#### ► ISC-3 links

ISC-3 links are for connections to z900, z800, and 9672 processors, and run at 100 or 200 MB/second. A maximum of 32 ISC-3 links may be used. These are packaged on I/O adapter cards, and each card can have two daughter cards. Each daughter card has two ISC links.

#### ICB and ISC links

The maximum number of external coupling links (ICB-2, ICB-3, ICB-4, active ISCs) is

32 per system. In addition, a maximum of 32 internal links (ICs) can be used.

The complete I/O configuration rules are more complex than outlined here. Consult your IBM representative for more specific and timely information.

You can order and install more physical channels than you can address. You can address 256 CHPIDs (that is, channels) with a Logical Channel Subsystem. As announced, two Logical Channel Subsystems may be used with the z990, allowing up to 512 CHPIDs (channels) to be addressed.<sup>3</sup> Each CHPID can be associated with a single channel. The

<sup>&</sup>lt;sup>3</sup> There are additional limitations if you use spanned channels.

physical channel (which, in practical terms, is a connector jack on an I/O adapter) is specified by its PCHID number. You can have more installed PCHIDs (physical channels) than CHPIDs. Your IOCDS definitions connect each CHPID to a PCHID. You must have all your defined CHPIDs connected to PCHIDs to have a valid IOCDS. However, you need not define all your installed PCHIDs (physical channels) in your IOCDS.

In theory, for example, you could install 69 ESCON adapters and enable 1024 channels,<sup>4</sup> each with a PCHID number. Using two Logical Channel Subsystem definitions to their fullest extent, you could only address 512 of these channels while using a given IOCDS. (Of course, you could define another IOCDS that used a different set of 512 channels.) If the z990 were to implement four Logical Channel Subsystems, for example, you could address a maximum of 1024 channels. That is, the *architecture* of the system allows more Logical Channel Subsystems than are implemented in the z990, and this architecture allows a large number of channels to be addressed as CHPIDs.

Logical Channel Subsystems are, in a sense, entities provided by the system firmware. They are discussed in more detail in "Channel subsystem" on page 32.

#### 2.8 I/O interfaces and identification

The I/O design and implementation is very similar to that of the z900. The primary difference is that the 1 GB/second STI links of the z900 have been replaced with 2.0 GB/second STI links. The general data flow structure is conceptually illustrated in Figure 2-5 on page 13, and works like this:

- Each book has 12 STI links, regardless of the number of PUs active in the book.

- ► An STI link (from a book) is connected to an STI-M card in an I/O cage. Two STI-M cards fit in a single slot in the I/O cage. These use slots 5, 14, 23, and 28 in the I/O cage. Slot 28 can hold only one STI-M card. This provides for a maximum of 7 STI-M cards in an I/O cage.

- ► Each STI-M card (in the I/O cage) is connected to four slots. The four slots driven by an STI-M card are its *domain*.

- ► Each book has 12 STI links. An I/O cage can have up to 7 STI connections (which means 7 domains). Many connection possibilities exist and some of the limitations are obvious. For example, a z990 model A08 cannot drive two fully-loaded I/O cages because it has only 12 STIs and the two cages need 14 STI connections.

- A z990 model D32 has 48 STI links. Three full I/O cages (the maximum possible) use 21 STI links.

- ▶ Directly connected ICB-4 links bypass the I/O cage and occupy a book STI connection.

- STI-2 and STI-3 adapters are used for ICB-2 and ICB-3 connections.

- Non-I/O adapters that occupy a slot in an I/O cage (such as a cryptographic adapter) are considered I/O adapters for this discussion.

Each possible "physical" CHPID port/connector has a PCHID number that is fixed by the physical location of the adapter and connector. An IOCDS associates a CHPID number to a PCHID number. An adapter in an I/O cage slot can provide a maximum of 16 CHPIDs. (The ESCON adapter does this, although only 15 can be used at one time.) There are a maximum of three I/O cages.<sup>5</sup> Each cage has a maximum of 28 slots. PCHID numbers are assigned as follows:

|               | P          | PCHID numbers |            |  |  |  |

|---------------|------------|---------------|------------|--|--|--|

| I/O cage slot | I/O Cage 1 | I/O Cage 2    | I/O Cage 3 |  |  |  |

<sup>&</sup>lt;sup>4</sup> Initially, the IBM configurator will not allow more than 512 channels to be ordered.

<sup>&</sup>lt;sup>5</sup> The numbering of the I/O cages is shown in Figure 2-2 on page 10.

```

1

100 - 10F

300 - 30F

500 - 50F

2

110 - 11F

310 - 31F

510 - 51F

120 - 12F

3

320 - 32F

520 - 52F

530 - 53F

4

130 - 13F

330 - 33F

6

140 - 14F

340 - 34F

540 - 54F

7

150 - 15F

350 - 35F

550 - 55F

8

160 - 16F

360 - 36F

560 - 56F

9

170 - 17F

370 - 37F

570 - 57F

180 - 18F

380 - 38F

580 - 58F

10

190 - 19F

390 - 39F

590 - 59F

11

12

1A0 - 1AF

3A0 - 3AF

5A0 - 5AF

13

1BO - 1BF

3B0 - 3BF

5B0 - 5BF

15

1CO - 1CF

3CO - 3CF

5CO - 5CF

16

1D0 - 1DF

3D0 - 3DF

5D0 - 5DF

1EO - 1EF

3E0 - 3EF

5E0 - 5EF

17

18

1F0 - 1FF

3F0 - 3FF

5F0 - 5FF

19

200 - 20F

400 - 40F

600 - 60F

20

210 - 21F

410 - 41F

610 - 61F

420 - 42F

21

220 - 22F

620 - 62F

230 - 23F

430 - 43F

630 - 63F

22

240 - 24F

440 - 44F

24

640 - 64F

450 - 45F

25

250 - 25F

650 - 65F

26

260 - 26F

460 - 46F

660 - 66F

270 - 27F

470 - 47F

670 - 67F

27

29

280 - 28F

480 - 48F

680 - 68F

290 - 29F

490 - 49F

690 - 69F

30

2A0 - 2AF

4A0 - 4AF

6A0 - 6AF

31

32

2B0 - 2BF

4B0 - 4BF

6B0 - 6BF

```

PCHID numbers used for direct book connections: 000-0FF

Note that slot numbers 5, 14, 23, and 28 are missing. These slots are used for STI connectors.

Consider an ESCON adapter in slot 15 of I/O cage 1. PCHID numbers 1C0 - 1CF are reserved for this slot. The first ESCON connector on the adapter (whether or not that particular port is enabled or used) is PCHID 1C0, the second connector is 1C1, and so forth. The PCHID numbers are fixed. The CHPID numbers are not fixed and can be arbitrarily assigned when an IOCDS is constructed. For example, an installation might decide to make PCHID 1C0 (the first ESCON channel in our example) CHPID 52 in LCSS 1.

#### I/O connections to books

Direct book connections (to STI ports) are used for ICB-4 channels. (These channels are used for connections to Coupling Facilities or other z990s.) There are 12 STI ports on a book, and a PCHID number is assigned to each one, as follows:

| book | PO  | PCHI |     |  |  |

|------|-----|------|-----|--|--|

| 0    | 010 | -    | 01B |  |  |

| 1    | 020 | -    | 02B |  |  |

| 2    | 030 | -    | 03B |  |  |

| 3    | 000 | -    | 00B |  |  |

These PCHIDs and connections do not involve I/O cages and are used for ICB-4 connections.

# 2.9 System control

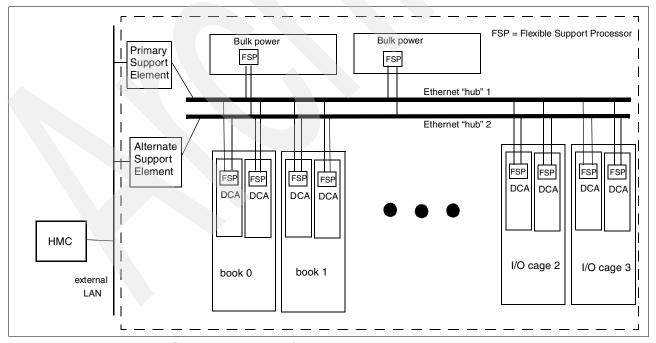

Figure 2-7 on page 20 provides a conceptual overview of the system control design. While the details have changed, the general structure for system control is similar to the z900.

Various system elements contain *Flexible Support Processors* (FSPs).<sup>6</sup> A Flexible Support Processor is a card based on the IBM Power PC microprocessor. An FSP connects to an internal Ethernet LAN (to communicate with the Support Elements) and provides a SubSystem Interface (SSI) for controlling components.<sup>7</sup> The SSI includes several UARTs, digital I/O lines, and a number of unique sensing and control lines and protocols.

A typical FSP operation is to control a power supply (shown as DCAs in the figure). A Support Element might send a command to the FSP to bring up the power supply. The FSP (using the SSI connections) would cycle the various components of the power supply, monitor the success of each step, monitor the resulting voltages, and report this status to the Support Element.

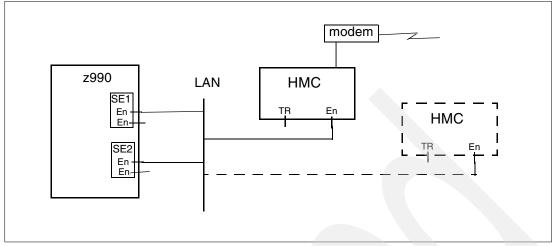

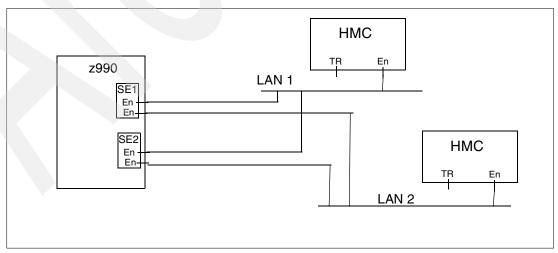

A z990 has more FSPs than indicated in the figure and the interconnections are more complex, but Figure 2-7 illustrates the general concepts involved. Most system elements are duplexed (for redundancy) and each element has an FSP. There are two internal Ethernet LANs and two Support Elements, again for redundancy. There is a crossover capability between the LANs, so that both Support Element can operate on both LANs.

The Support Elements, in turn, are connected to another (external) LAN (Ethernet or token ring) and the Hardware Management Consoles (HMCs) are connected to this external LAN. There can be one or more HMCs. In a production environment, the system hardware is normally managed from the HMCs. If necessary, the system can be managed from either Support Element. Several or all HMCs can be disconnected without affecting system operation.

Figure 2-7 Conceptual overview of system control elements

<sup>&</sup>lt;sup>6</sup> These were informally known as *cage controllers* in earlier systems.

<sup>&</sup>lt;sup>7</sup> More detailed descriptions may refer to SSI-M and SSI-S notations, corresponding to master and slave functions.

The operation of the internal LANs and the FSPs is checked by a Network Heart Beat (NHB) function that uses complementary programs in the Support Elements and the FSPs to verify correct operation and to trigger alternative reassignments when necessary.

# 2.10 Power and cooling

A z990 system uses three-phase 200-480 VAC power. A small A08 system uses approximately 6.8 KW (if all I/O adapter slots are filled), while a very large D32 system uses up to 21.4 KW. Two power feed cables are connected to two internal bulk power units that provide power for the system. The system can continue operation after a failure of one of these units. They are designed such that the system will continue to operate after a failure of one phase of the incoming power supply.

Internal functions adjust the power factor to almost 1.0, with little harmonic content. (This complies with increasing demands, sometimes in the form of binding requirements, for *building-friendly* power supplies.)

Incoming power is converted to high voltage DC and this is distributed to the subsidiary power units that convert it to the various voltages need by the controllers, cages, books, and I/O adapters. Very large currents are needed at low voltages and it is not practical to directly distribute the low voltage supplies throughout the system.

As a overview statement, everything in the power system is duplexed. Each book (up to four) exists on its own power boundary, meaning that it is possible to remove power on a book without affecting other books.<sup>8</sup> Two additional power supply units are installed in the processor cage as part of an upgrade to the next higher model.

The processor cage (containing the books) uses 1.2, 1.5, 2.5, and 3.4 volt supplies. (The 1.2 volt requirement is up to 700 amperes!) The I/O cages use 1.8, 2.5, 3.3, 3.4, 5.0, and 24 volt supplies.

Units known as DCAs convert the distributed high voltage to various low voltages. Slightly different DCAs are used in the processor cage and the I/O cages. Up to eight DCAs are used for the processor cage (two for each book), and each I/O cage contains two DCAs. Each DCA has a Flexible Support Processor that is part of the system control function discussed in "System control" on page 20.

#### **2.10.1 Cooling**

The z990 uses refrigeration cooling for the MCMs in the books. Everything else is air-cooled.

The refrigeration package is a Modular Cooling Unit (MCU). A single MCU has two cooling loops and cools the MCMs in one or two books. A z990 model B16 or larger will have two MCUs. The MCUs are not redundant. If an MCU fails such that MCM temperatures rise above specified levels, the system cycle time is automatically slowed down. (The cycle time is the same for all books, and a slowdown affects all books.) MCMs produce less heat when run slower, and an integrated backup air-cooling mechanism (with fans) is sufficient at the slower speed.

System slowdown (after an MCM failure) is in steps, depending on the temperatures in the books. The maximum slowdown is 8%.

<sup>&</sup>lt;sup>8</sup> There are many implications to removing a book. This discussion is only about the power aspects.

The two cooling loops in an MCU are controlled independently. For example, a book connected to one cooling loop can be removed or added without affecting the operation of another book being cooled by the other loop.<sup>9</sup>

The other components of the system (I/O cages, power supplies, memory in the books, and so forth) are air-cooled. A sophisticated arrangement of fans (Air Movement Devices, or AMDs) and sensors provides the operation. Fan speeds are variable and are controlled to maintain the required cooling.

The MCU refrigeration units are air-cooled; that is, their heat sink is into the general airflow of the z990 system. The total heat produced by the system ranges from approximately 23,000 BTUs (small system, 6.8 KW) to 73,000 BTUs (21.4 KW). This heat load must be managed by the raised-floor air system.

# 2.11 Concurrent changes

A typical z990 may replace several older systems. One consequence of this is that any disruption of z990 service will probably affect more applications than on previous systems. You might view repair and configuration changes as having several levels:

- ► A concurrent repair or configuration change takes place while the system is running and the affected operating systems are running. That is, IPLs or a Power-on Reset (POR) are not required.

- ► A slightly more complex change, without POR or IPLs, would involve taking a CHPID offline and back online to activate a change to it.

- ► A more disruptive change might require IPLing one or more operating systems, but without a POR. This implies that some operating systems (in their own LPARs) are not affected.

- ► A POR affects the complete system for a relatively short time and requires all LPARs to be IPLed again. (These IPL procedures will take varying amounts of time, depending on the complexity of the environments being started.)

- ► A change or repair that requires *power off* affects the complete system, of course, and implies more time than a POR.

The z990 has many internal, automatic, self-repairing functions. These are usually concurrent functions and may not be visible to any operating system. Many system upgrades and repairs are concurrent activities. Over a number of years, IBM has steadily increased the number of repair actions and configuration changes that can be done concurrently, and this direction is continued with the z990.

#### 2.12 Instruction set