Dino Quintero Wei Li Wainer dos Santos Moschetta Mauricio Faria de Oliveira Alexander Pozdneev

# NVIDIA CUDA on IBM POWER8: Technical overview, software installation, and application development

## **Overview**

The exploitation of general-purpose computing on graphics processing units (GPUs) and modern multi-core processors in a single heterogeneous parallel system has proven highly efficient for running several technical computing workloads. This applied to a wide range of areas such as chemistry, bioinformatics, molecular biology, engineering, and big data analytics.

Recently launched, the IBM® Power System S824L comes into play to explore the use of the NVIDIA Tesla K40 GPU, combined with the latest IBM POWER8™ processor, providing a unique technology platform for high performance computing.

This IBM Redpaper<sup>™</sup> publication discusses the installation of the system, and the development of C/C++ and Java applications using the NVIDIA CUDA platform for IBM POWER8.

**Note:** CUDA stands for *Compute Unified Device Architecture*. It is a parallel computing platform and programming model created by NVIDIA and implemented by the GPUs that they produce.

The following topics are covered:

- ► Advantages of NVIDIA on POWER8

- ► The IBM Power Systems S824L server

- ► Software stack

- System monitoring

- Application development

- ► Tuning and debugging

- ► Application examples

# Advantages of NVIDIA on POWER8

The IBM and NVIDIA partnership was announced in November 2013, for the purpose of integrating IBM POWER®-based systems with NVIDIA GPUs, and enablement of GPU-accelerated applications and workloads. The goal is to deliver higher performance and better energy efficiency to companies and data centers.

This collaboration produced its initial results in 2014 with:

- ► The announcement of the first IBM POWER8 system featuring NVIDIA Tesla GPUs (IBM Power Systems<sup>TM</sup> S824L).

- ► The release of CUDA 5.5 for POWER8.

- ► The availability of several applications and tools to leverage GPU acceleration and CUDA (for example, IBM XL C/C++ compilers, IBM Java, and others).

More applications, middlewares, and workloads from various fields announced upcoming support for GPU acceleration on IBM Power Systems.

The computational capability provided by the combination of NVIDIA Tesla GPUs and IBM POWER8 systems enable workloads from scientific, technical, and high performance computing to run on data center hardware. In most cases, these workloads were run on supercomputing hardware. This computational capability is built on top of massively parallel and multithreaded cores with NVIDIA Tesla GPUs and IBM POWER8 processors, where processor-intensive operations were offloaded to GPUs and coupled with the system's high memory-hierarchy bandwidth and I/O throughput.

An overview of the NVIDIA Tesla GPU is provided in "NVIDIA Tesla K40 GPU" on page 10. You can learn more at the following website:

http://nvidia.com/tesla

For more information about the IBM POWER8 processor and systems, refer to "The IBM Power Systems S824L server" on page 2.

Moreover, the development and portability of GPU-accelerated applications for IBM Power Systems with NVIDIA GPUs is made easier with the availability of CUDA and little-endian mode on POWER8, which increases the commonality with other popular architectures, and the growing ecosystem built around the OpenPOWER Foundation. You can learn more about OpenPOWER at the following website:

http://openpowerfoundation.org

In summary, IBM Power Systems with NVIDIA GPUs provides a computational powerhouse for running applications and workloads from several scientific domains, and for processing massive amounts of data, with eased application development and portability. All of this builds upon the strong ecosystems of the NVIDIA CUDA architecture and the OpenPOWER Foundation.

# The IBM Power Systems S824L server

In October 2014, IBM announced a new range of systems targeted at handling massive amounts of computational data<sup>1</sup>.

See IBM Provides Clients Superior Alternative to x86-Based Commodity Servers, found at: http://www.ibm.com/press/us/en/pressrelease/45006.wss

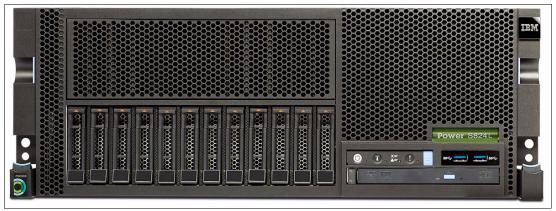

IBM Power Systems S824L<sup>2</sup> (see Figure 1) is the first IBM Power Systems server that features NVIDIA GPU. This offering delivers a new class of technology that maximizes performance and efficiency for scientific, engineering, Java, big data analytics, and other technical computing workloads. Designed to empower the ecosystem of open source development, these new servers support little-endian Ubuntu Linux running in bare metal mode.

Figure 1 Front view of the IBM Power Systems S824L server

The IBM POWER8 processor was designed for data-intensive technical computing workloads, big data and analytics applications. All aspects of its design are optimized to deal with today's exploding data sizes. The POWER8 cache hierarchy was architected to provide data bandwidth that is suitable for running large data sets through and to accommodate their large footprints.

The POWER8 processor comes in two versions. One version is targeted toward large SMP systems at the enterprise level. The other is specifically designed for scale-out servers that are building blocks for current and future IBM high performance computing systems. The two latter chips are installed in pairs in a dual-chip module (DCM). DCM connects its chips with SMP links and plugs into a socket in the planar of the system. Functionally, DCM works as a single processor, and the operating system considers DCM as a NUMA node. The IBM POWER8 scale-out servers contain one or two sockets populated with DCMs.

The IBM Power Systems S824L server (model 8247-42L) is a two-socket system. The server is available in two-processor configurations:

- ► Two 10-core 3.42 GHz POWER8 DCMs (20 cores per system)

- ► Two 12-core 3.02 GHz POWER8 DCMs (24 cores per system)

The IBM Power Systems S824L server has 16 slots for DDR3 ECC memory<sup>3</sup> (8 slots per DCM) and supports memory modules of 16 GB, 32 GB, and 64 GB. The maximum configurable system memory is 1 TB. The form factor for the memory modules is Custom DIMM (CDIMM).

<sup>&</sup>lt;sup>2</sup> The model name follows a simple convention. The first letter ("S") stands for "scale-out", the first digit indicates POWER8 processor, the second digit is for the number of sockets, the third digit reflects the server height in standard rack units, and the trailing "L" letter indicates "scale-out/Linux". IBM Power scale-out/Linux servers are designed specifically to run the Linux operating system. If you are interested in running the IBM AIX® or IBM i operating system on POWER scale-out servers, you need to consider server models that do not have the letter "L" suffix in their names (S814, S822, and S824: as of writing time of this IBM Redpaper publication).

<sup>&</sup>lt;sup>3</sup> Error-correcting code (ECC) memory is a type of random access memory that can detect and correct spontaneous runtime failures of memory cells or memory access logic.

**Note:** In general, the introduction of new technology in memory modules may increase the maximum system memory configurable for a system. However, that is subject to support, compatibility, and possibly other restrictions.

The minimum system configuration includes one NVIDIA GPU. The maximum system configuration is two GPUs.

The S824L planar features 11 PCle Gen3 slots:

- ► Four ×16 slots (one or two are used for NVIDIA GPU cards)

- ► Seven ×8 slots (one is used for the integrated LAN adapter)

The server has a rack-mounted form factor and takes 4U (four units) of rack space. It is depicted on Figure 1 on page 3. The lower-left frontal part of the server features 12 small form factor bays for internal storage based on HDDs (hard disk drives) or SSDs (solid-state drives). Two USB 3.0 ports and a DVD bay are visible at the lower-right front part of the server.

For more detailed information about the server options, search the IBM Offering Information website for the IBM Power Systems S824L:

http://www.ibm.com/common/ssi/index.wss

The official technical documentation for the IBM Power Systems S824L server is at:

http://www.ibm.com/support/knowledgecenter/8247-42L/p8hdx/8247 421 landing.htm

To acquire a better technical understanding of the IBM Power Systems S824L server and its reliability, availability, and serviceability features, refer to the following IBM Redbooks publication: *IBM Power Systems S824L Technical Overview and Introduction*, REDP-5139.

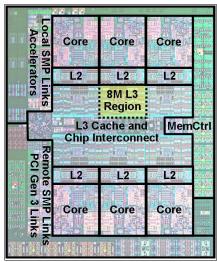

## The IBM POWER8 processor chip

The POWER8 processor is fabricated with IBM 22 nanometer (22 nm) silicon-on-insulator (SOI) technology using copper interconnects and 15 layers of metal. The scale-out version of the POWER8 chip shown in Figure 2 on page 5 contains six cores<sup>4</sup> and is 362 square millimeters (mm) in size. Each core has 512 KB of static RAM (SRAM) second-level cache (L2), and 8 MB of embedded DRAM (eDRAM) third-level cache (L3). The L3 cache is shared among all cores of the chip. The chip also includes a memory controller with four memory interfaces, PCle Gen3 controllers, SMP interconnect, hardware accelerators, and coherent accelerator processor interface (CAPI). The interconnection system links all components within the chip.

<sup>&</sup>lt;sup>4</sup> The number of cores activated depends on a server offering.

Figure 2 The POWER8 scale-out processor chip

The SMP fabric of the IBM POWER8 scale-out chip has two types of links:

- "X" bus connects a pair of chips to form a dual-chip module (DCM)

- "A" bus provides intersocket communications

Two POWER8 scale-out chips are installed in pairs in a DCM that plugs into a socket in a system planar of a computing server. In a maximum configuration, 12 POWER8 cores of a DCM share 96 MB of L3 cache and two memory controllers address 512 GB of system memory through eight memory interfaces.

#### **POWER8** core

The POWER8 is a 64-bit processor based on the IBM Power (Performance Optimization With Enhanced RISC<sup>5</sup>) Instruction Set Architecture (ISA) Version 2.07. The POWER8 computing core is a superscalar out-of-order eight-way simultaneously multithreaded (SMT)<sup>6</sup> microprocessor. POWER8 is the first processor based on the IBM POWER Architecture that supports little-endian as well as big-endian byte ordering in virtualized and non-virtualized (or bare-metal) mode<sup>7</sup>.

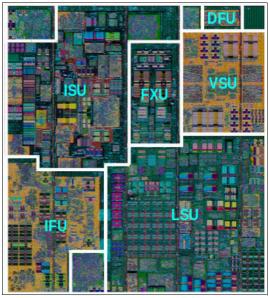

The primary components of a POWER8 core are shown in Figure 3 on page 6:

- ► Instruction fetch unit (IFU)

- Instruction sequencing unit (ISU)

- ► Load/store unit (LSU)

- Fixed point unit (FXU)

- Vector and scalar unit (VSU)

- ► Decimal floating point unit (DFU)

FISC is an acronym for "reduced instruction set computer". The first prototype computer to use RISC architecture was designed by IBM researcher John Cocke and his team in the late 1970s. For the historical perspective, see <a href="http://www.ibm.com/ibm/history/ibm100/us/en/icons/risc">http://www.ibm.com/ibm/history/ibm100/us/en/icons/risc</a>

<sup>&</sup>lt;sup>6</sup> Simultaneous multithreading capabilities of POWER8 processor core allow eight independent software threads to efficiently share the core resources. This mode is known as SMT8. In a single-threaded mode, almost all the resources of the highly parallel POWER8 core are used by the single thread.

$<sup>^{7}</sup>$  The byte ordering (big-endian or little-endian) for a storage access is specified by the operating system.

Figure 3 The IBM POWER8 processor core

On each cycle, the IFU of a POWER8 core selects a thread and fetches eight quadword-aligned<sup>8</sup> instructions from the 32 KB eight-way first-level instruction cache into a thread instruction buffer. POWER8 instructions are always 4 bytes long and word-aligned. As a result, an eight-instruction block is 32-byte long.

In SMT modes, the POWER8 thread priority logic selects two threads per cycle for instruction group formation. Groups are independently formed by reading a maximum of three nonbranches and one branch from the instruction buffer of each thread, for a total of eight instructions. After group formation, the simple instructions are immediately decoded, and the complex instructions are routed to special microcode hardware that breaks them into a series of simple internal operations.

The POWER8 core dispatches instructions on a group basis as soon as all resources are available for the instructions in a group. In SMT modes, two groups are dispatched independently. The ISU dispatches eight instructions per cycle into three separate issue queues:

- A unified queue

- ► A branch issue queue

- A condition register issue queue

The ISU is also responsible for register renaming and instruction completion.

POWER8 core saves dispatched instructions in the issued queues and then issues them to the execution units. Instructions can be issued in order or out of order from all of these queues. An instruction in the issue queue is selected for issuing when all source operands for that instruction are available. The issue queues together can issue a total of ten instructions per cycle:

- ▶ One branch instruction to the branch execution unit

- One condition register logical instruction to the condition register execution unit

- ► Two fixed-point instructions to the FXU

- Two load/store and two load instructions to the LSU

- Two instructions to the VSU

<sup>8</sup> Halfword, word, doubleword, and quadword are 2-, 4-, 8-, and 16-byte memory entries, respectively. One, two, three, and four least significant bits of a halfword-, word-, doubleword-, and quadword-aligned memory address are zeros, accordingly.

In addition to load/store operations, the LSU can accept and execute simple fixed-point instructions coming from each of its four execution pipelines.

VSU includes the following subunits:

- ► Two single precision vector floating point units (FPUs)

- ► Two double precision vector FPUs

- ► Two scalar FPUs

- ► Two fixed-point vector units

- One decimal floating point unit (DFU)

- ► One cryptographical operations unit

VSU vector subunits operate on 128-bit registers. To manipulate vectors, VSU implements vector multimedia extension (VMX) and vector scalar extension (VSX) instructions<sup>9</sup>. The POWER8 core is able to issue up to two fused multiply-add instructions on vectors in each cycle, thereby delivering 16 single precision or eight double precision floating point operations per cycle during peak workloads.

## **PCI Express**

The IBM POWER8 server system components are connected through the Peripheral Component Interconnect Express Gen3 (PCI Express Gen3 or PCIe Gen3) bus.

In server systems, some PCIe devices are connected directly to the PCIe Gen3 buses on the processors, and other devices are connected to these buses through PCIe Gen3 switches. PCIe slots are used to plug in devices such as InfiniBand cards, 10 GbE network interface cards, Fibre Channel adapters, SAS cards for internal disks and external SAS ports. Some of the PCIe slots are Coherent Accelerator Processor Interface (CAPI)-enabled to connect custom acceleration engines (for example, (field-programmable gate arrays (FPGAs)) to the coherent fabric of the POWER8 chip.

The IBM POWER8 scale-out chip has 24 PCIe Gen3 full duplex lanes that provide 7.877 Gbit/s of effective bandwidth in each direction. The total effective theoretical bandwidth for a DCM is calculated as follows:

2 chips  $\times$  24 lanes  $\times$  7.877 Gbit/s  $\times$  2 directions = 94.524 Gbyte/s

**Note:** The bandwidth listed here might appear slightly differently from other materials. In our case, we consider the bandwidth overhead originated from the PCIe Gen3 encoding scheme. We also avoid rounding where possible.

## **Energy awareness**

The energy that is required to power and cool servers contributes significantly to the overall operational efficiency of the computing infrastructure. To address this challenge, IBM developed the EnergyScale™ technology for IBM Power Systems servers. This technology helps to control the power consumption and performance of POWER8 servers. For more details, refer to the IBM EnergyScale for POWER8 processor-based systems paper at:

http://public.dhe.ibm.com/common/ssi/ecm/en/pow03125usen/POW03125USEN.PDF

The IBM POWER8 chip has an embedded IBM PowerPC® 405 processor with 512 KB of SRAM. This processor known as an on-chip controller (OCC) runs a real-time control firmware. The purpose of the OCC is to respond timely to workload variations. The OCC adjusts the per-core frequency and voltage based on activity, thermal, voltage, and current sensors. The OCC real-time OS was released as open source software.

<sup>9</sup> The IBM VMX and VSX instructions implement and extend the AltiVec specifications that were introduced to the Power ISA at its 2.03 revision.

See the open-power/OCC site:

http://github.com/open-power/occ

## On-chip accelerators

The IBM POWER8 processor has the on-chip accelerators that provide the following functions:

- ► On-chip encryption

- ► On-chip compression

- ► On-chip random number generation

The Linux kernel uses on-chip accelerators through specialized drivers<sup>10</sup>.

The on-chip cryptography accelerator (also known as the *cryptographical module*) provides high-speed encryption capabilities. The operating system can employ this facility to offload certain latency tolerant operations, for example, file system encryption and securing Internet Protocol communications.

The on-chip compression engine (sometimes referred to as *memory compression module*) was designed as a facility that helps the operating system to compress the least frequently used virtual memory pages.

The on-chip random number generator (typically abbreviated as RNG) provides the operating system with the source of hardware-based random numbers. This generator was architected to be cryptographically stronger than software-based pseudo-random number generators. In some instances, there can also be a performance advantage.

In addition to on-chip accelerators, each core has built-in functions that facilitate the implementation of cryptographical algorithms. An application developer can leverage these capabilities by employing compiler intrinsics in their source code or writing in assembly language.

#### Coherent accelerator processor interface

Many computing workloads can benefit from running on a specialized hardware like field-programmable gate arrays (FPGAs) or GPUs rather than on a general-purpose processor. Traditionally, external accelerators communicate with the processor through the I/O bus, which follows the model of I/O device operation. To simplify the interaction between processor and accelerators, IBM introduced the CAPI with the POWER8 processor. CAPI attaches devices to the SMP fabric of the POWER8 chip. As a result, CAPI enables off-chip accelerators to access the main system memory and participate in the system memory coherence protocol as a peer of other caches in the system. In other words, CAPI allows a specialized accelerator to be seen as just an additional processor in the system.

The conforming accelerator is to be plugged into a standard PCIe Gen3 slot marked as CAPI-enabled. The CAPI coherency protocol is tunneled over a standard PCIe Gen3 bus.

## **Memory subsystem**

The IBM POWER8 processor was designed to have a strong memory subsystem to be capable of meeting the bandwidth, latency, and capacity demands of data and compute intensive applications.

<sup>10</sup> Available only in selected offerings.

Each core of the POWER8 processor has private caches of first (L1) and second level (L2):

- ▶ 32 KB of L1 instruction cache

- ▶ 64 KB of L1 data cache

- ▶ 512 KB of L2 unified cache

Cache memory of a third level (L3) is shared between all cores of the POWER8 chip. A core has faster access to its local 8 MB L3 cache region.

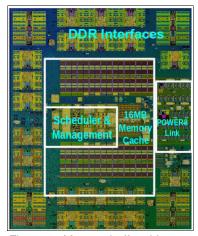

The scale-out version of the POWER8 processor chip has one memory controller with four memory interfaces. Memory slots are populated with custom DIMM (CDIMM) memory modules. *CDIMM* is a memory card that houses a set of industry standard dynamic random access memory (DRAM) memory chips and a memory buffer chip. The memory controller of a processor accesses system memory through that external memory buffer chip. The memory buffer chip isolates processor memory controller from the interaction with the actual DRAM memory chips. At the time this publication was written, the POWER8 server offerings include DDR3 memory options, whereas the described technology allows easy transition to DDR4 memory later. Figure 4 illustrates the POWER8 memory organization.

Figure 4 POWER8 memory organization

The memory buffer chip shown in Figure 5 consists of the following components:

- ► POWER8 processor link

- Memory cache

- ► Memory scheduler

- Memory manager

- ► DDR3 interfaces

Figure 5 Memory buffer chip

The 16 MB memory buffer chip cache constitutes the fourth level (L4) of cache hierarchy. The memory scheduler supports prefetch and write optimization. The memory manager is responsible for RAS decisions<sup>11</sup> and energy management.

## Hardware transactional memory

The *transactional memory* (TM) is a computer science concept that was created to facilitate the design of multithreaded algorithms. The TM makes a series of loads and stores appear as a single atomic operation, a *transaction*, that either succeeds or fails. The TM is primarily intended to be used in situations where software engineers typically employ locks in order to ensure atomicity of a set of operations.

There are algorithms in which the probability of a memory conflict between application threads is negligible. Nevertheless, even in such cases, software engineers need to employ locks in order to ensure that the algorithm is always correct. The use of locks in frequently executed pieces of code might have a dramatic impact on performance.

One algorithmic approach that allows you to avoid acquiring locks in this situation is a lock elision technique. A thread needs to mark the beginning and end of a *transaction* on shared variables with the TM directives or instructions provided by a programming language or system software. In an optimistic execution scenario, there are no conflicts, and transactions always succeed. In an expected highly improbable conflict situation, the TM reports that a transaction has failed. In this case, an algorithm developer can either try a transaction again with a TM, or fall back to a lock-based if-then-else branch in the code.

Historically, the TM was first implemented as a pure software-based mechanism. Hardware support for the TM became a commercial reality only recently. To the best of our knowledge, the first commercially available product with the hardware transactional memory (HTM) capabilities was the IBM Blue Gene/Q® (BG/Q) supercomputer in 2011. The BG/Q compute chip was based on PowerPC A2 processor cores and implemented transactional execution primarily in the L2 cache, which served as the point of coherence. In 2012, IBM started to ship IBM zEnterprise® EC12 (zEC12) IBM System z® mainframe solutions that targeted business audiences. With the zEC12 microprocessor, IBM offered a multiprocessor transactional support. At the time this publication was written, the latest IBM product with support for HTM is the POWER8 processor. The first POWER8 based server systems were shipped in 2014. The IBM POWER architecture support for HTM includes instructions and registers that control the transactional state of a thread. The Power ISA Version 2.07 specification also describes the behavior of transactions regarding the execution and memory models of the processor. It also includes more complex behaviors such as suspend mode, which allows non-transactional operations inside a transaction.

### **NVIDIA Tesla K40 GPU**

The NVIDIA Tesla K40 GPU is based on Kepler architecture version GK110B that supports the CUDA compute capability 3.5. It can deliver 1.43 Tflop/s (peak) performance for double-precision floating point operations and 4.29 Tflop/s for single-precision.

The Kepler GK110B architecture highlights the following improvements over previous generations:

- Streaming Multiprocessor (SMX): Features a new generation of Streaming Multiprocessor (SM)

- ▶ Dynamic parallelism: Ability to launch nested CUDA kernels

- ► Hyper-Q: Allows several CPU threads or processes to dispatch CUDA kernels concurrently

<sup>11</sup> The RAS decisions deal with reliability, availability, and serviceability features and functions.

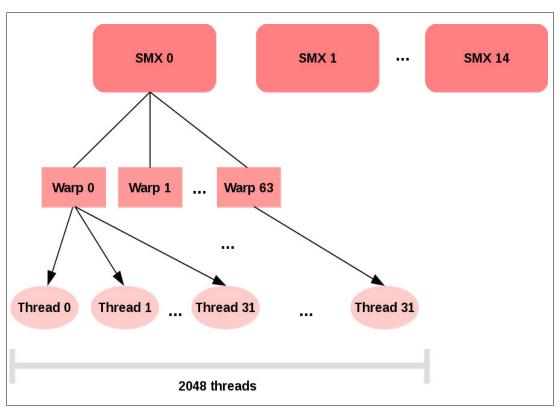

As a result, the NVIDIA Tesla K40 GPU can be logically viewed as follows:

- ► Fifteen SMX multiprocessors, each with:

- 192 single-precision CUDA cores

- 64 double-precision units

- 32 special function units (SFU)

- 32 load/store units

- 16 texture filtering units

- ► Four warp schedulers and eight instruction dispatch units per SMX

- ► Six 64-bit memory controllers per GPU

Each thread can address up to 255 registers. The single and double-precision arithmetic units are fully compliant with IEEE 754-2008 standard, including an implementation of fused multiply-add (FMA).

A warp is a group of 32 parallel threads that are scheduled to run in an SMX multiprocessor. The maximum number of warps per SMX is 64, and it is capable of issuing and executing four warps simultaneously. Figure 6 shows the organization between multiprocessors, warps, and threads with the Tesla K40 GPU.

Figure 6 NVIDIA Tesla K40 GPU warps organization

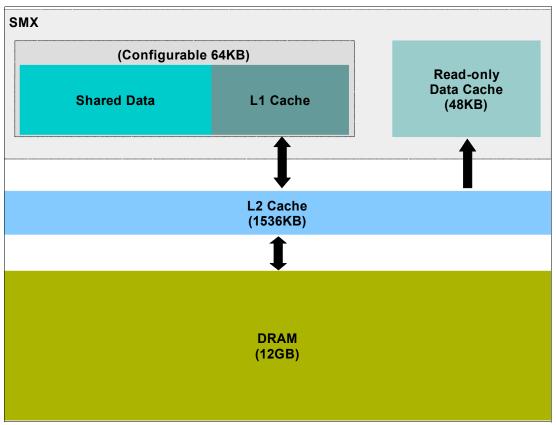

The memory hierarchy is shown in Figure 7 on page 12 and has the following levels:

▶ 64 KB configurable shared memory and L1 cache per multiprocessor.

There are three possible configurations:

- 48 KB shared memory and 16 KB L1 cache

- 16 KB shared memory and 48 KB L1 cache

- 32 KB shared memory and 32 KB L1 cache

The shared memory is accessed in words of 8 bytes.

- 48 KB read-only data cache per multiprocessor

- 1536 KB L2 cache

- ► 12 GB DRAM (GDDR5)

Figure 7 NVIDIA Tesla K40 GPU memory hierarchy

Memory errors in the shared memory, L1/L2 cache, and DRAM are remedied with the use of an error correcting code (ECC) implementation of a single-error correct or double-error detect (SECDED) scheme. The read-only data cache uses parity checking to detect problems and a single-error correction mechanism, which consists of reload data from the L2 cache.

The Hyper-Q technology (also known as *CUDA Streams*) is controlled by hardware that offers up to 32 connections to the work queues.

The NVIDIA GPU Boost feature is designed to speed up applications by taking advantage of the power headroom on the graphical card. A user application may not take full advantage of a 235 W Tesla K40 power budget. The NVIDIA GPU Boost feature allows users to change the default SMX clock frequency to higher values, while maintaining power consumption below the allowed limit. The processor clock options vary from 324 MHz up to 875 MHz with 745 MHz being the default value. The memory clock frequency is mostly kept at 3 GHz in any profile, except for the lowest 324 MHz processor clock frequency option as shown in Table 1 on page 13. Because 745 MHz is the base processor clock frequency, the 810 MHz and 857 MHz processor clock frequency options are used to boost performance.

Table 1 Tesla K40 GPU supported clocks

| Memory clock (MHz) | Processor clock (MHz) |

|--------------------|-----------------------|

| 3004               | 875                   |

| 3004               | 810                   |

| 3004               | 745                   |

| 3004               | 666                   |

| 324                | 324                   |

Detailed rationale and information about NVIDIA Tesla K40 Boost can be found in the NVIDIA GPU Boost for Tesla K40 Passive and Active Boards - Application Note found at this site:

http://www.nvidia.com/object/tesla\_product\_literature.html

One ×16 PCI Express Gen3 slot is used to connect a GPU card to the host system.

The Tesla K40 GPU has four compute modes:

- Prohibited: Not available for compute applications

- Exclusive Thread: Only one process and thread can use the GPU at a time

- ► Exclusive Process: Only one process can use the GPU at the time, but its threads can create work concurrently

- ► Default: Multiple processes/threads can use the GPU simultaneously

Example 1 shows the output of the *deviceQuery* application that comes with the CUDA toolkit samples (see "NVIDIA CUDA Toolkit code samples" on page 55). The command provides more information about the NVIDIA Tesla K40 GPU of the IBM Power Systems S824L server, which is discussed throughout this paper.

Example 1 Output of the deviceQuery application (some output omitted)

```

$ ./deviceQuery

<...>

Detected 2 CUDA Capable device(s)

Device 0: "Tesla K40m"

CUDA Driver Version / Runtime Version

6.5 / 5.5

CUDA Capability Major/Minor version number:

3.5

Total amount of global memory:

11520 MBytes (12079136768 bytes)

(15) Multiprocessors, (192) CUDA Cores/MP:

2880 CUDA Cores

GPU Clock rate:

745 MHz (0.75 GHz)

Memory Clock rate:

3004 Mhz

Memory Bus Width:

384-bit

L2 Cache Size:

1572864 bytes

Maximum Texture Dimension Size (x,y,z)

1D=(65536), 2D=(65536, 65536), 3D=(4096, 4096,

4096)

Maximum Layered 1D Texture Size, (num) layers

1D=(16384), 2048 layers

Maximum Layered 2D Texture Size, (num) layers

2D=(16384, 16384), 2048 layers

Total amount of constant memory:

65536 bytes

Total amount of shared memory per block:

49152 bytes

Total number of registers available per block: 65536

32

Maximum number of threads per multiprocessor:

2048

Maximum number of threads per block:

1024

```

```

Max dimension size of a thread block (x,y,z): (1024, 1024, 64)

Max dimension size of a grid size (x,y,z): (2147483647, 65535, 65535)

Maximum memory pitch:

2147483647 bytes

Texture alignment:

512 bytes

Concurrent copy and kernel execution:

Yes with 2 copy engine(s)

Run time limit on kernels:

Integrated GPU sharing Host Memory:

No

Support host page-locked memory mapping:

Yes

Alignment requirement for Surfaces:

Yes

Device has ECC support:

Enabled.

Device supports Unified Addressing (UVA):

Device PCI Domain ID / Bus ID / location ID:

2 / 1 / 0

Compute Mode:

< Default (multiple host threads can use ::cudaSetDevice() with device simultaneously) >

Device 1: "Tesla K40m"

<... output ommitted ...>

Compute Mode:

< Default (multiple host threads can use ::cudaSetDevice() with device simultaneously) >

> Peer access from Tesla K40m (GPU0) -> Tesla K40m (GPU1) : No

> Peer access from Tesla K40m (GPU1) -> Tesla K40m (GPU0) : No

deviceQuery, CUDA Driver = CUDART, CUDA Driver Version = 6.5, CUDA Runtime Version = 5.5,

NumDevs = 2, Device0 = Tesla K40m, Device1 = Tesla K40m

Result = PASS

```

## Software stack

This section describes the installation of the software stack for running CUDA applications on POWER8 with the following components:

- ► CUDA: NVIDIA CUDA Toolkit v5.5 (CUDA 5.5) for POWER8

- ► Operating system: Ubuntu Server 14.10 in non-virtualized mode

- ► C/C++ compilers: GCC<sup>12</sup> 4.9 or IBM XL C/C++ compilers v13.1.1

- ► Java: IBM SDK, Java Technology Edition 7.1-2.0<sup>13</sup>

Note: NVIDIA announced an upcoming release of CUDA 7.0 as of this writing.

You should expect similarity with the content described in this paper, with changes where appropriate (for example, version numbers in command lines, and program output).

The supported operating systems for CUDA 7.0 on POWER8 now include Ubuntu Server 14.04.2 LTS, in addition to Ubuntu Server 14.10 (both in non-virtualized mode).

It also describes the installation of the cross-platform development packages for running a development environment on an x86-64 computer with CUDA applications running on the POWER8 system (remotely), with the following components:

- ► CUDA: NVIDIA CUDA Toolkit v5.5 (CUDA 5.5) for POWER8 (cross-platform on x86-64)

- ► IDE: NVIDIA NSight Eclipse Edition version 5.5.0

- Operating system: Ubuntu 14.04 LTS

<sup>&</sup>lt;sup>12</sup> This is Ubuntu Server GCC. The Advance Toolchain GCC is not supported by CUDA at the time of this writing.

<sup>&</sup>lt;sup>13</sup> That is, Version 7 Release 1, Service Refresh 2 Fix Pack 0.

This section also covers the following prerequisites for performing the operating system installation on POWER8: Intelligent Platform Management Interface (IPMI)

Additionally, it describes the configuration of CPU Frequency Scaling

## **Intelligent Platform Management Interface**

The following steps consist of setting an IPMI password for the system, and instructions to manage the system using IPMI.

For performing the steps described in this section, access the system's Advanced System Management Interface (ASMI) as administrator:

- Point your web browser to the system's Flexible Service Processor (FSP) address: https://fsp-address

- 2. Log in as administrator (User ID: admin).

## Steps to set the IPMI password

The following steps are used to set the IPMI password:

- 1. Expand Login Profile and click Change Password.

- 2. From the User ID to change list, select IPMI.

- 3. In the Current password for user ID admin field, enter the administrator password.

- 4. In the New password for user and New password again fields, enter the IPMI password.

- 5. Click Continue.

## Managing the system using IPMI

The IPMItool is a command-line interface program for managing IPMI devices using the network. For example, the interface can be used to power a system on and off, and access its console 14.

You can install the IPMItool from your workstation Linux distribution packages. For example, in Ubuntu:

```

$ sudo apt-get install ipmitool

```

Or you can also build it from the source, which is available at the following site:

```

http://sourceforge.net/projects/ipmitool

```

Use the IPMItool version 1.8.14 or later, which has the latest fixes and improvements. You can check the version with the command:

```

$ ipmitool -V

```

The following list contains common ipmitool commands:

► Power on:

```

$ ipmitool -I lanplus -H fsp-address -P ipmi-password power on

```

► Power off:

```

$ ipmitool -I lanplus -H fsp-address -P ipmi-password power off

```

<sup>&</sup>lt;sup>14</sup> Also known as Serial over LAN (SOL) session.

#### ► Power cycle (Power off, then Power on):

\$ ipmitool -I lamplus -H fsp-address -P ipmi-password power cycle

#### ► Power status:

\$ ipmitool -I lanplus -H fsp-address -P ipmi-password power status

#### ► Open console session:

\$ ipmitool -I lanplus -H fsp-address -P ipmi-password sol activate

#### ► Close console session:

\$ ipmitool -I lanplus -H fsp-address -P ipmi-password sol deactivate

You can also close the current console session with the following keystrokes:

On a non-SSH connection:

Enter,

$$\sim$$

(tilde<sup>15</sup>), . (period)

Note: This command might close a Secure Shell (SSH) connection, which would leave the console session open.

On an SSH connection:

```

Enter, ~ (tilde), ~ (tilde), . (period)

```

Note: This command leaves the SSH connection open, and closes the console session.

#### ► Reset the FSP:

\$ ipmitool -I lanplus -H fsp-address -P ipmi-password bmc reset cold

► Sensors values:

```

$ ipmitool -I lanplus -H fsp-address -P ipmi-password sdr list full

```

► Specific sensor value:

```

$ ipmitool -I lanplus -H fsp-address -P ipmi-password sdr entity XY[.Z]<sup>16</sup>

```

**Note:** The IPMItool might not be available for some platforms. For an alternative IPMI utility (not covered in this publication), refer to the IPMI Management Utilities project at this link:

http://sourceforge.net/projects/ipmiutil

#### **Ubuntu Server**

The supported operating system for CUDA 5.5 on POWER8 is Ubuntu Server 14.10 in non-virtualized mode.

**Note:** The supported operating systems for CUDA 7.0 on POWER8 now include Ubuntu Server 14.04.2 LTS, in addition to Ubuntu Server 14.10 (both in non-virtualized mode).

To install Ubuntu Server on the IBM Power system S824L, you can choose one of the following methods:

- ► CD/DVD installation

- Network installation (netboot)

<sup>&</sup>lt;sup>15</sup> On keyboards with dead-keys (some non-english languages), the tilde mark requires 2 keystrokes: tilde and space.

<sup>&</sup>lt;sup>16</sup> Sensor entity: XY (entity ID) or XY. Z (entity ID and instance ID); listed with the sdr elist full IPMI command (see the fourth field of its output).

Both methods use an IPMI console session for performing the installation process.

Petitboot (system bootloader) is used to boot the installation media. Some basic instructions for operating it are as follows:

- ► To move the selection between elements, use the up/down or tab/shift-tab keys

- ► To select an entry, confirm ("click") a button, and mark a check box, move the selection to it and press the Enter or Space key

- ► To return from a window (discard changes), press the Esc key

- ► To enter long text strings, you can use the "paste" feature of your terminal

- ► The bottom lines display some shortcut keys/help

## Power on and open the console session

The following steps are used to power on and open the console session:

- 1. Power on (or power cycle, if already on) the system:

- \$ ipmitool -I lanplus -H fsp-address -P ipmi-password power on # or cycle

- 2. Open a console session:

- \$ ipmitool -I lanplus -H fsp-address -P ipmi-password sol activate

- 3. Wait a few minutes for the *Petithoot* window.

#### **CD/DVD** installation

The following steps consist of downloading an Ubuntu Server installation ISO image, burning it to a CD/DVD disc, and booting the CD/DVD disc:

1. Download the Ubuntu Server installation image (ubuntu-version-server-ppc64e1.iso), which can be found at<sup>17</sup>:

```

\label{eq:http://cdimage.ubuntu.com/releases/} \rightarrow \textit{version} \rightarrow \text{release} or

```

$http://ubuntu.com \rightarrow Download \rightarrow Server \rightarrow POWER8 \rightarrow Ubuntu Server version$

Burn (write) the ISO image to a CD/DVD disc.

General instructions are available at:

http://help.ubuntu.com/community/BurningIsoHowto

Example 2 shows how to burn the ISO image to a CD/DVD disc in the command-line interface.

#### Example 2 Burning an ISO to CD/DVD disc using the wodim command-line program

```

$ dmesg | grep writer # check the CD/DVD writer device (usually /dev/sr0)

$ sudo apt-get install wodim

$ sudo wodim -v dev=/dev/sr0 ubuntu-version-server-ppc64el.iso

```

- 3. Insert the CD/DVD disc into the system's optical drive.

- 4. In the Petitboot window, select Rescan devices.

- 5. Wait a few seconds for a new entry (from the Ubuntu Server CD/DVD disc).

- 6. Select the new entry.

- 7. Wait for the installer to start, and proceed with the Ubuntu Server installation.

Direct link (version 14.10 "Utopic Unicorn"): http://cdimage.ubuntu.com/releases/14.10/release/ubuntu-14.10-server-ppc64el.iso

## **Network installation (netboot)**

The following steps consist of configuring and testing the network, and booting the network installation files.

#### Network configuration

To perform the network configuration:

- 1. In the **Petitboot** window, select **System Configuration** (this takes you to the **Petitboot System Configuration** window).

- 2. From the **Network** list, select one of the following network configuration options:

- DHCP on all active interfaces

- DHCP on a specific interface

- Static IP configuration

- 3. Provide the network settings in the required fields below the **Network** list, if any.

Note: The DNS server field is required if the DNS servers are not provided by DHCP.

- DHCP on all active interfaces: None

- DHCP on a specific interface: Device

- Static IP configuration: Device, IP/mask, Gateway, DNS server(s)

- 4. Select OK.

#### Network configuration test

The following steps are used to perform the network configuration test:

- 1. In the Petitboot window, select Exit to shell (this takes you to the Petitboot shell).

- 2. Perform a network test (see Example 3 for a successful ping test).

Example 3 Network configuration test in the Petitboot shell

```

# ping -c1 ubuntu.com

PING ubuntu.com (91.189.94.40): 56 data bytes

64 bytes from 91.189.94.40: seq=0 ttl=47 time=73.004 ms

--- ubuntu.com ping statistics ---

1 packets transmitted, 1 packets received, 0% packet loss

round-trip min/avg/max = 73.004/73.004/73.004 ms

```

Enter the exit command to return to the Petitboot window.

# exit

If the network configuration test is successful, proceed to the next steps. Otherwise, repeat the network configuration and test steps, and verify your network settings.

**Tip:** You can use normal Linux network commands (for example, **ping**, **ip**, **ifconfig**, **route**) in the Petitboot shell in order to debug network configuration issues.

#### New entry for netboot files

The netboot files are the kernel (vmlinux file) and initial RAM disk (initrd.gz file). You will need the URL (link address) for both, which can be obtained at 18:

$\label{eq:http://cdimage.ubuntu.com/netboot/} \rightarrow \textit{version} \rightarrow \text{ppc64el} \rightarrow \text{ubuntu-installer} \rightarrow \text{ppc64el}$

or:

- 1. Copy the URLs for the kernel (vml inux file) and initial RAM disk (initrd.qz file).

- 2. In the **Petitboot** window, press the **n** key to create a new entry (this takes you to the **Petitboot Option Editor** window).

- 3. From the Device list, select Specify paths/URLs manually.

- 4. In the **Kernel** field, enter the URL for *vmlinux*:

http://ports.ubuntu.com/ubuntu-ports/dists/utopic-updates/main/installer-ppc64e l/current/images/netboot/ubuntu-installer/ppc64el/vmlinux

5. In the **Initrd** field, enter the URL for *initrd.gz*:

http://ports.ubuntu.com/ubuntu-ports/dists/utopic-updates/main/installer-ppc64e l/current/images/netboot/ubuntu-installer/ppc64el/initrd.gz

- 6. Optional: If you have a preseed<sup>19</sup> file (used for automatic installation), enter the related options in the **Boot arguments** field.

- 7. Select **OK** (this takes you back to the **Petitboot** window).

- 8. Select **User item 1** (new entry).

- 9. The bottom line changes to:

```

Info: Booting <url>

```

- 10. Wait for the files to download.

- 11. The bottom lines change to:

```

The system is going down NOW!

Sent SIGTERM to all processes

Sent SIGKILL to all processes

```

12. Wait for the installer to start, and proceed with the Ubuntu Server installation.

#### **Ubuntu Server installer**

The Ubuntu Server installation process is standard, regardless of the GPU cards or IBM Power Systems S824L. Refer to the Ubuntu Server installation documentation for instructions:

Overview

http://help.ubuntu.com  $\rightarrow$  Ubuntu  $version \rightarrow$  Ubuntu Server Guide  $\rightarrow$  Installation

► Ubuntu Installation Guide:

$\begin{array}{l} \texttt{http://help.ubuntu.com} \to \texttt{Ubuntu} \ \textit{version} \to \texttt{Installing Ubuntu} \to \texttt{IBM/Motorola} \\ \texttt{PowerPC}^{20} \end{array}$

http://ports.ubuntu.com/ubuntu-ports/dists/utopic-updates/main/installer-ppc64el/current/images/netboot/ubuntu-installer/ppc64el

<sup>18</sup> Direct link (version 14.10 "Utopic Unicorn"):

<sup>&</sup>lt;sup>19</sup> For more information, check Ubuntu Installation Guide, Appendix B: Automating the installation using preseeding.

<sup>20</sup> This documentation is more targeted at PowerPC desktop systems, but provides some general instructions.

During installation, in the **Software selection** window, select **OpenSSH Server** to access the system through SSH upon first boot.

After the installation is finished, the system reboots. See the next section for verifying and configuring the autoboot settings.

## **Autoboot configuration**

By default, Petitboot will automatically boot (autoboot) from any disk/network interface within 10 seconds. That is reasonable if only one operating system is installed, but you might want to change/configure it depending on your preferences:

- 1. In the **Petitboot** window, select **System configuration** (this takes you to the **Petitboot System Configuration** window).

- 2. From the **Autoboot** list, select one of the following autoboot options:

- Do not autoboot (wait for user selection)

- Autoboot from any disk/network device (default)

- Only Autoboot from a specific disk/network device

- 3. Provide values for the required fields below the Autoboot list, if any.

- Only Autoboot from a specific disk/network device: Select the device from the disk/net list

**Note:** You can check the disk devices with operating systems detected in the Petitboot window.

4. Select OK.

Petitboot does not automatically boot any entry now because of user interaction. This time, it is necessary to boot the Ubuntu Server manually.

- 5. Select Ubuntu.

- 6. Wait for the operating system to boot (login prompt).

#### Verifying the network connectivity

The network settings are inherited from the installation process. Therefore, networking should be working at this point. You can verify the network connectivity with the following commands.

From another system:

- Ping the system:

- \$ ping -c1 system-address

- Open an SSH connection:

- \$ ssh user@system-address

If the ping and SSH connection tests are successful, proceed to the next steps. Otherwise, verify and configure the system's network settings, and restart the network interface (Example 4).

Example 4 The network configuration file, its manual page, and a network interface restart

- \$ sudo nano /etc/network/interfaces

- \$ man interfaces

- \$ sudo ifdown ethX

- \$ sudo ifup ethX

#### Close the console session

If you can open SSH connections to the system, it is possible to perform the next steps using SSH, which is more convenient. It is a good practice to close the IPMI console session.

In order to close the IPMI console session, use one of the methods that are described in "Intelligent Platform Management Interface" on page 15.

#### **CUDA** toolkit

In order to install the CUDA toolkit, perform the following steps:

1. Verify that the GPU cards are detected (Example 5 shows two GPU cards).

#### Example 5 Verifying the GPU cards with Ispci

```

$ 1spci | grep -i nvidia

0002:01:00.0 3D controller: NVIDIA Corporation GK110BGL [Tesla K40m] (rev a1)

0006:01:00.0 3D controller: NVIDIA Corporation GK110BGL [Tesla K40m] (rev a1)

```

2. Install basic development packages (CUDA toolkit dependencies):

```

$ sudo apt-get install build-essential

```

3. Download the DEB package of the CUDA repository for Ubuntu 14.10 on POWER8, which is available in the Downloads section of the NVIDIA CUDA Zone website:

```

http://developer.nvidia.com/cuda-downloads-power8 → Ubuntu 14.10 DEB

```

**Note:** On future CUDA releases, the mentioned files should be available in the normal NVIDIA CUDA downloads page, under the Linux POWER8 tab:

http://developer.nvidia.com/cuda-downloads → Linux POWER8.

#### \$ waet

http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1410/ppc64el/cuda-repo-ubuntu1410 5.5-54 ppc64el.deb

4. Install the DEB package:

```

$ sudo dpkg -i cuda-repo-ubuntu1410 5.5-54 ppc64el.deb

```

It inserts the CUDA repository in the package manager configuration file (Example 6).

#### Example 6 Package manager configuration file for the CUDA repository

```

$ cat /etc/apt/sources.list.d/cuda.list

deb http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1410/ppc64el /

```

5. Update the package manager's definitions:

```

$ sudo apt-get update

```

Finally, install the CUDA toolkit using the cuda meta-package (Example 7 on page 22).

The *cuda* meta-package makes the appropriate packages of the CUDA toolkit version available for the architecture, and their dependencies.

Among other steps, the installation builds and configures the kernel modules for the NVIDIA graphics driver (which requires the basic development tools that were installed previously).

The support for Dynamic Kernel Module Support (DKMS) is installed by default (specified as a dependency of the nvidia-340 package), so that the kernel modules are automatically rebuilt on kernel upgrades if required.

#### Example 7 Installation of the cuda meta-package

```

$ sudo apt-get install cuda

<...>

The following NEW packages will be installed:

acpid cuda cuda-5-5-power8 cuda-command-line-tools-5-5-power8 <...>

cuda-cusparse-5-5-power8 cuda-cusparse-dev-5-5-power8 <...>

cuda-misc-headers-5-5-power8 cuda-npp-5-5-power8 <...>

dkms libcuda1-340 nvidia-340 nvidia-340-dev nvidia-340-uvm

<...>

Do you want to continue? [Y/n] y

<...>

Loading new nvidia-340-340.50 DKMS files...

First Installation: checking all kernels...

Building only for 3.16.0-28-generic

Building for architecture ppc64el

Building initial module for 3.16.0-28-generic

Done.

<...>

DKMS: install completed.

**********************************

Please reboot your computer and verify that the nvidia graphics driver is loaded.

If the driver fails to load, please use the NVIDIA graphics driver .run installer

to get into a stable state.

**************************

<...>

```

7. Configure the search paths for the CUDA commands and libraries, making the setting available to all users and persistent across reboots (Example 8).

#### Example 8 Configuration of search paths for CUDA commands and libraries

```

$ echo 'export PATH=$PATH:/usr/local/cuda-5.5-power8/bin' | sudo tee

/etc/profile.d/cuda.sh

$ echo /usr/local/cuda-5.5-power8/lib64 | sudo tee /etc/ld.so.conf.d/cuda.conf

$ sudo ldconfig

```

**Note:** The changes to the command search path environment variable (PATH) have no effect in the current shell (the shared library-related changes do). To apply it to the current shell run the following command:

```

$ source /etc/profile.d/cuda.sh

```

If the shared library search path is not configured correctly, CUDA applications linked to CUDA shared libraries fail, as shown in Example 9.

Example 9 Failure of CUDA applications with misconfigured shared library search path

```

<application>: error while loading shared libraries: <cuda library>.so.x.x:

cannot open shared object file: No such file or directory

```

**Note:** Refer to the Linux Getting Started Guide (also known as the NVIDIA CUDA Getting Started Guide for Linux)  $\rightarrow$  Installing CUDA Development Tools  $\rightarrow$  Install the NVIDIA CUDA Toolkit  $\rightarrow$ Package Manager Installation  $\rightarrow$  Environment Setup, for a different approach:

http://developer.nvidia.com/cuda-downloads

```

$ export PATH=$PATH:/usr/local/cuda-5.5-power8/bin

$ export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:/usr/local/cuda-5.5-power8/lib64

```

These are useful export entries if you do not have superuser privileges in the system. The downside is that this is not available to all users and this is not permanent across reboots. Also, the shared library search path may be inadvertently overridden when building/running non-system wide installed software.

In order to make this setting permanent across reboots, for some users, they must add these lines to their ~/.bashrc file.

- 8. Reboot the system:

- \$ sudo reboot

- 9. After rebooting, verify that the *nvidia* module is loaded and the GPU devices are available (Example 10).

**Note:** The kernel message nvidia: module verification failed is not an error. The message refers to loading modules with a proprietary license (see lines above it).

Example 10 Verification of nvidia module and GPU status

```

$ dmesg | grep -i nvidia

[<...>] nvidia: module license 'NVIDIA' taints kernel.

[<...>] nvidia: module license 'NVIDIA' taints kernel.

[<...>] nvidia: module verification failed: signature and/or required key missing

- tainting kernel

[<...>] nvidia 0002:01:00.0: enabling device (0140 -> 0142)

[<...>] nvidia 0006:01:00.0: enabling device (0140 -> 0142)

[<...>] [drm] Initialized nvidia-drm 0.0.0 20130102 for 0002:01:00.0 on minor 0

[<...>] [drm] Initialized nvidia-drm 0.0.0 20130102 for 0006:01:00.0 on minor 1

[<...>] NVRM: loading NVIDIA UNIX ppc64le Kernel Module 340.50 <...>

$ 1smod | grep nvidia

nvidia 13941291 0

drm

382761 2 nvidia

$ nvidia-smi --list-gpus

GPU 0: Tesla K40m (UUID: GPU-9c8168e0-dc96-678f-902f-3997a6f2dfc5)

GPU 1: Tesla K40m (UUID: GPU-6d42c48f-2d92-c254-9703-7218aa15fa40)

```

10.Perform a simple test with the CUDA sample *simpleCUFFT*, which uses CUDA libraries and GCC (default compiler), as shown in Example 11 on page 24<sup>21</sup>.

<sup>&</sup>lt;sup>21</sup> Shell linebreaks added for clarity.

```

$ cp -r /usr/local/cuda-5.5-power8/samples/ ~/cuda-samples

$ cd ~/cuda-samples/7_CUDALibraries/simpleCUFFT/

$ make

/usr/local/cuda-5.5-power8/bin/nvcc -ccbin g++ -I../../common/inc -m64

-gencode arch-compute 20,code-sm 20 -gencode arch-compute 30,code-sm 30 -gencode

arch=compute 35,code=\"sm 35,compute 35\" -o simpleCUFFT.o -c simpleCUFFT.cu

/usr/local/cuda-5.5-power8/bin/nvcc -ccbin g++ -m64

-o simpleCUFFT

simpleCUFFT.o -lcufft

mkdir -p ../../bin/ppc64le/linux/release

cp simpleCUFFT ../../bin/ppc64le/linux/release

$ ../../bin/ppc64le/linux/release/simpleCUFFT

[simpleCUFFT] is starting...

GPU Device 0: "Tesla K40m" with compute capability 3.5

Transforming signal cufftExecC2C

Launching ComplexPointwiseMulAndScale<<< >>>

Transforming signal back cufftExecC2C

```

For more information, refer to the Linux Getting Started Guide (also known as NVIDIA CUDA Getting Started Guide for Linux), available in the Downloads section of the NVIDIA CUDA Zone website:

http://developer.nvidia.com/cuda-downloads

## IBM XL C/C++ Compiler

To install the IBM XL C/C++ Compiler, perform the following steps:

- 1. Install the basic development packages (IBM XL C/C++ Compiler dependencies):

- \$ sudo apt-get install build-essential

- 2. Install the DEB packages provided with your installation media (Example 12).

Example 12 Installation of the XL C/C++ Compiler packages

```

$ cd <path to IBM XL C/C++ deb-packages>

$ sudo dpkg -i xlc*.deb libxlc*.deb libxlmass*.deb libxlsmp*.deb # or *.deb <...>

Setting up xlc-license.13.1.1 (13.1.1.0-141105) ...

Setting up libxlc (13.1.1.0-141105) ...

Setting up libxlmass-devel.13.1.1 (13.1.1.0-141105) ...

Setting up libxlmass-devel.8.1.0 (8.1.0.0-141027) ...

Setting up libxlsmp (4.1.0.0-141010) ...

Setting up libxlsmp-devel.4.1.0 (4.1.0.0-141010) ...

Setting up xlc.13.1.1 (13.1.1.0-141105) ...

Please run 'sudo /opt/ibm/xlC/13.1.1/bin/xlc_configure' to review the license and configure the compiler.

```

3. To review the license and configure the compiler, enter:

```

$ sudo /opt/ibm/x1C/13.1.1/bin/x1c configure

```

*Note*: For non-interactive installations, see Example 13 on page 25.

```

$ echo 1 | sudo /opt/ibm/xlC/13.1.1/bin/xlc_configure

<...>

International License Agreement <...>

<...>

Press Enter to continue viewing the license agreement, or, Enter "1" to accept the agreement, "2" to decline it or "99" to go back to the previous screen, "3" Print.

[INPUT] ==> 1

<...>

update-alternatives: using /opt/ibm/xlC/13.1.1/bin/xlc to provide /usr/bin/xlc (xlc) in auto mode

<...>

INFORMATIONAL: GCC version used in

"/opt/ibm/xlC/13.1.1/etc/xlc.cfg.ubuntu.14.04.gcc.4.8.2" -- "4.8.2"

INFORMATIONAL: /opt/ibm/xlC/13.1.1/bin/xlc_configure completed successfully

```

4. Perform a simple test with the CUDA sample *simpleCUFFT*, which uses CUDA libraries and IBM XL C++ (using the -ccbin x1C option for nvcc, which can be defined in CUDA samples with the make variable GCC), as shown in Example 14.

A few points:

- The compiler warning is not an error; it refers to analysis of the source code.

- The output of running simpleCUFFT is the same as shown in Example 11 on page 24<sup>22</sup>.

Example 14 Building and running simpleCUFFT with IBM XL C++

```

Note: this step may have been performed in the other example (GCC).

$ cp -r /usr/local/cuda-5.5-power8/samples/ ~/cuda-samples

$ cd ~/cuda-samples/7 CUDALibraries/simpleCUFFT/

$ make clean

rm -f simpleCUFFT.o simpleCUFFT

rm -rf ../../bin/ppc64le/linux/release/simpleCUFFT

$ make GCC=x1C

/usr/local/cuda-5.5-power8/bin/nvcc -ccbin xlC -I../../common/inc -m64

-gencode arch-compute 20,code-sm 20 -gencode arch-compute 30,code-sm 30 -gencode

arch=compute 35,code=\"sm 35,compute 35\" -o simpleCUFFT.o -c simpleCUFFT.cu

../../common/inc/helper cuda.h:493:9: warning: 4 enumeration values not handled in

switch: 'CUFFT INCOMPLETE PARAMETER LIST', 'CUFFT INVALID DEVICE',

'CUFFT PARSE ERROR'... [-Wswitch]

switch (error)

1 warning generated.

/usr/local/cuda-5.5-power8/bin/nvcc -ccbin x1C

-m64

-o simpleCUFFT

simpleCUFFT.o -lcufft

mkdir -p ../../bin/ppc64le/linux/release

cp simpleCUFFT ../../bin/ppc64le/linux/release

$ ../../bin/ppc64le/linux/release/simpleCUFFT

<...>

```

<sup>&</sup>lt;sup>22</sup> Shell linebreaks added for clarity.

For more information, refer to the IBM Knowledge Center website:

http://ibm.com/support/knowledgecenter  $\rightarrow$  Rational  $\rightarrow$  C and C++ Compilers  $\rightarrow$  XL C/C++ for Linux  $\rightarrow$  XL C/C++ for Linux version  $\rightarrow$  Installation Guide

#### Java

To install the IBM Developer Kit for Linux, Java Technology Edition, perform the following steps:

Download the IBM Developer Kit for Linux, Java Technology Edition, which is available at:

http://ibm.com/developerworks/java/jdk/ → in row Linux, Downloads → Java SE

Version 7 → in row 64-bit IBM POWER (LE), Download Now

**Note:** Download the SDK file *ibm-java-ppc64le-sdk-*<*version*>.*bin*. (This is not the SDK in the archive format, and not the JRE only, because JRE is included in the SDK.)

- 2. Make the file executable:

- \$ chmod +x ibm-java-ppc64le-sdk-7.1-2.0.bin

- 3. Perform the installation with one of the following methods:

- Interactive: To review the license and options:

- \$ sudo ./ibm-java-ppc64le-sdk-7.1-2.0.bin

- Non-interactive: Using default options:

- \$ sudo ./ibm-java-ppc64le-sdk-7.1-2.0.bin -i silent

- 4. Configure the environment and command search path for Java (Example 15)<sup>23</sup>.

Example 15 Configuring the environment and command search path for Java

```

$ cat <<"EOF" | sudo tee /etc/profile.d/ibm-java.sh

export JAVA_HOME=/opt/ibm/java-ppc64le-71

export PATH=$PATH:$JAVA_HOME/bin:$JAVA_HOME/jre/bin

EOF</pre>

```

**Note:** The changes to the shell environment (PATH) have no effect in the current shell. To apply the changes to the current shell, run:

\$ source /etc/profile.d/ibm-java.sh

5. Verify the Java virtual machine and Java Compiler commands (Example 16).

Example 16 Verifying the Java virtual machine and Java Compiler commands

```

$ java -version

java version "1.7.0"

Java(TM) SE Runtime Environment (build px16470_27sr2-20141101_01(SR2))

IBM J9 VM (build 2.7, JRE 1.7.0 Linux ppc64le-64 Compressed References

20141031_220034 (JIT enabled, AOT enabled)

J9VM - R27_Java727_SR2_20141031_1950_B220034

JIT - tr.r13.java_20141003_74587.02

GC - R27_Java727_SR2_20141031_1950_B220034_CMPRSS

J9CL - 20141031_220034)

```

<sup>&</sup>lt;sup>23</sup> The first EOF delimiter is quoted ("EOF") to avoid variable expansion.

```

JCL - 20141004_01 based on Oracle 7u71-b13

$ javac -version

javac 1.7.0-internal

```

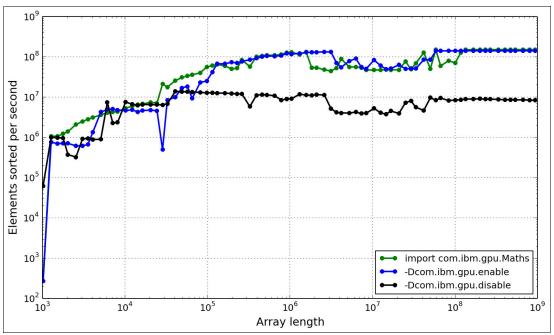

6. Perform a simple test that uses *com.ibm.gpu* classes (discussed in "CUDA and IBM Java" on page 40) to list the available GPUs (Example 17 shows two GPUs).

Notes about the java command options:

- Xmso512k: Java requires an operating system thread stack size of at least 300 KB for CUDA functionality (otherwise, an exception is triggered), as of this writing

- - Dcom.ibm.gpu.enable: Enables CUDA functionality

- - Dcom.ibm.gpu.verbose: Verbose logging of the CUDA functionality

Example 17 Java application with the com.ibm.gpu classes to list the available GPUs

```

$ cat > ListGPUs.java <<EOF</pre>

import com.ibm.gpu.*;

public class ListGPUs {

public static void main(String[] args) throws Exception {

System.out.println(CUDAManager.getInstance().getCUDADevices());

E0F

$ javac ListGPUs.java

$ java -Xmso512k -Dcom.ibm.gpu.enable ListGPUs

[com.ibm.gpu.CUDADevice@5530ad1, com.ibm.gpu.CUDADevice@611a71b1]

$ java -Xmso512k -Dcom.ibm.gpu.enable -Dcom.ibm.gpu.verbose ListGPUs

[IBM GPU]: [<...>]: System property com.ibm.gpu.enable=

[IBM GPU]: [<...>]: Enabling sort on the GPU

[IBM GPU]: [<...>]: Discovered 2 devices

[IBM GPU]: [<...>]: Providing identifiers of discovered CUDA devices, found: 2

devices

[IBM GPU]: [<...>]: Discovered devices have the following identifier(s):

[com.ibm.gpu.CUDADevice@5530ad1, com.ibm.gpu.CUDADevice@611a71b1

```

For more information about the development of Java applications that use GPUs, refer to the IBM Knowledge Center website:

```

http://ibm.com/support/knowledgecenter \rightarrow WebSphere \rightarrow IBM SDK, Java Technology Edition \rightarrow IBM SDK, Java Technology Edition \rightarrow Developing Java applications \rightarrow Writing Java applications that use a graphics processing unit

```

For more information about the installation and configuration of the IBM JDK, refer to the IBM Knowledge Center website:

http://ibm.com/support/knowledgecenter  $\rightarrow$  WebSphere  $\rightarrow$  IBM SDK, Java Technology Edition  $\rightarrow$  IBM SDK, Java Technology Edition  $version \rightarrow$  Linux User Guide for IBM SDK, Java Technology Edition,  $version \rightarrow$  Installing and configuring the SDK and Runtime Environment

Also see the IBM developerWorks® pages for IBM Developer Kit for Linux, Java Technology Edition:

http://ibm.com/developerworks/java/jdk/linux

**Note:** The terms "IBM Developer Kit for Linux, Java Technology Edition" and "IBM SDK, Java Technology Edition" are used interchangeably in this section.

## CPU frequency scaling

Linux provides CPU frequency scaling with the cpufreq mechanism. It can adjust the processors' clock frequency over time, according to certain policies, called *governors*.

The default scaling governor in Ubuntu Server is ondemand, which dynamically adjusts CPU frequency according to system load, on a processor-core level. This enables power-savings without compromising performance. A core's frequency is maintained low when idle, and increased under load.

On highly-utilized HPC systems, the preferable scaling governor is performance, which statically sets CPU frequency to the highest available. This ensures that a core is clocked at maximal frequency at all times, and eliminates any frequency-scaling overhead and jitter.

The cpufreg settings are per-CPU (hardware thread) files placed in:

/sys/devices/system/cpu/cpu<number>/cpufreq/

Although the cpufreq settings are exposed *per-CPU* (or *per-hardware thread*), they are actually *per-core* on POWER8 (that is, equal among all hardware threads in a core). This is reflected in the related\_cpus file, as seen in Example 18, which shows that CPU (or hardware thread) 0 shares settings with other CPUs (hardware threads) of its core (its eight hardware threads, in SMT8 mode).

Example 18 The related\_cpus file

\$ cat /sys/devices/system/cpu/cpu0/cpufreq/related\_cpus

0 1 2 3 4 5 6 7

As an example, the current scaling governor can be displayed/changed by using the scaling\_governor file, and the available scaling governors are displayed in the scaling available governors file (Example 19).

Example 19 Accessing the scaling\_governor and scaling\_available\_governors files

\$ cat /sys/devices/system/cpu/cpu0/cpufreq/scaling\_governor

ondemand

\$ cat /sys/devices/system/cpu/cpu0/cpufreq/scaling\_available\_governors

conservative userspace powersave ondemand performance

\$ echo performance | sudo tee

/sys/devices/system/cpu/cpu0/cpufreq/scaling\_governor

performance

\$ cat /sys/devices/system/cpu/cpu0/cpufreq/scaling\_governor

performance

#### Set the scaling governor to performance on all CPUs

The cpufrequtils package provides tools for managing cpufreq settings on all CPUs/hardware-threads (system-wide), and making changes persistent across reboots.

- 1. Install cpufrequtils:

- \$ sudo apt-get install cpufrequtils

- 2. Add the line GOVERNOR="performance" to the file /etc/default/cpufrequtils. This makes the setting persistent across reboots. You can either use a text editor or the following command:

- \$ echo 'GOVERNOR="performance" | sudo tee -a /etc/default/cpufrequtils

- 3. Disable the system's default ondemand governor setting:

- \$ sudo update-rc.d ondemand disable

- 4. Finally, activate the performance governor without rebooting the system:

- \$ sudo service cpufrequtils start

You can use the **cpufreq-info** command for obtaining status of the cpufreq settings. See Example 20 to verify the number of CPUs/hardware-threads that are running with a certain governor.

Example 20 Number of CPUs with respective scaling governor

```

$ cpufreq-info | grep 'The governor' | uniq -c

160 The governor "performance" <...>

```

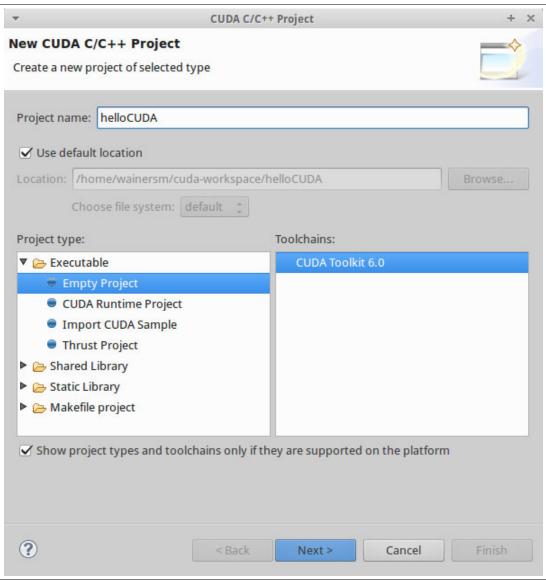

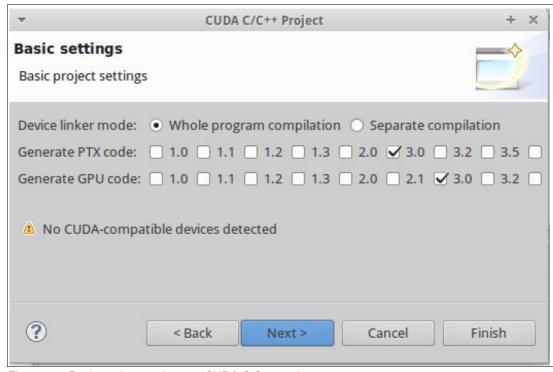

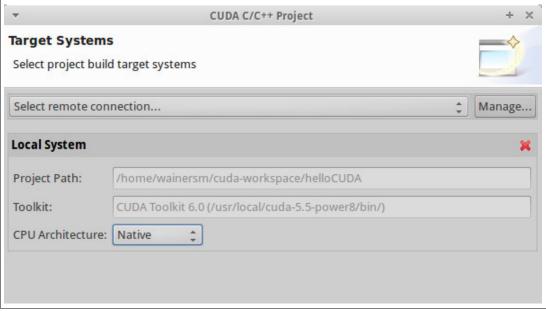

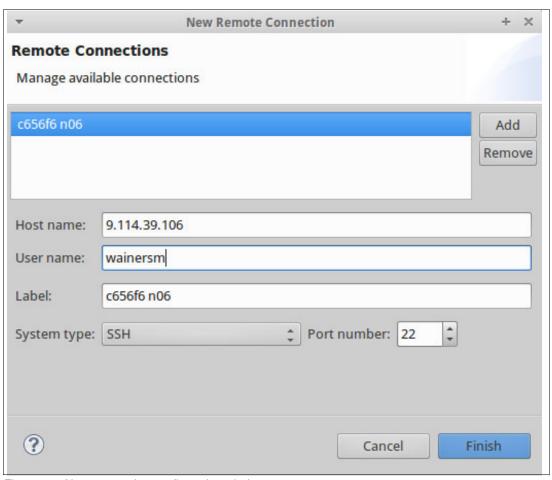

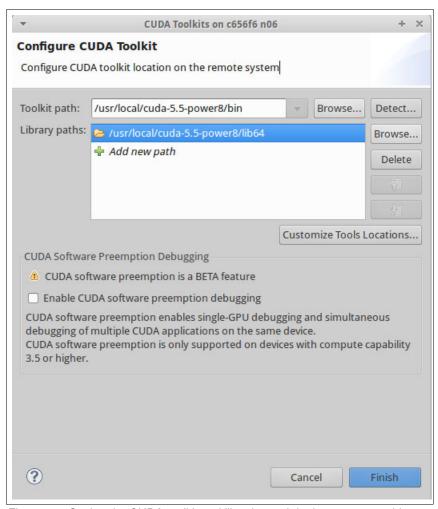

## **CUDA** cross-platform development

The CUDA cross-platform development tools run in a x86-64 computer, and the CUDA applications run on the POWER8 system (remotely). The supported operating system is Ubuntu 14.04 LTS for amd64.

**Note:** Installation instructions for Ubuntu 14.04 LTS for amd64 are not covered in this paper. Refer to the Ubuntu Installation Guide at:

<code>http://help.ubuntu.com</code>  $\to$  <code>Ubuntu 14.04 LTS</code>  $\to$  <code>Installing Ubuntu</code>  $\to$  <code>AMD64 & Intel EM64T.</code>

You may download Ubuntu 14.04 LTS for amd64, at:

http://ubuntu.com  $\to$  Download  $\to$  Desktop  $\to$  Ubuntu 14.04(.x) LTS  $\to$  Flavour: 64-bit  $\to$  Download.

To install the cross-platform development packages, it is required to add the target system's architecture as a foreign architecture in the package manager. This is a requirement for the CUDA packages.

For CUDA cross-platform development in POWER8 systems, add the ppc64e1 architecture (the architecture string for the 64-bit PowerPC instruction-set in little-endian mode in Ubuntu and Debian distributions) as a foreign architecture for the package manager (dpkg). This does not interfere with the primary architecture of the package manager, which is still amd64 (similarly, for the 64-bit version of the x86 instruction-set). The user might observe that i 386 (similarly, for the x86 instruction-set) is already a foreign architecture by default, which enables the installation of 32-bit packages. Refer to Example 21.

Example 21 Adding ppc64el as a foreign architecture in Ubuntu 14.04 LTS for amd64

```

Primary architecture:

$ dpkg --print-architecture

amd64

Foreign architectures:

$ dpkg --print-foreign-architectures

i386

$ sudo dpkg --add-architecture ppc64e1

$ dpkg --print-foreign-architectures

i386

ppc64e1

```

Proceed to install the CUDA repository package (which inserts the CUDA repository in the package manager configuration files), and update the package manager's definitions (Example 22).

#### Example 22 Installing the CUDA repository package

```

$ wget

http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1404/x86_64/cuda-rep

o-ubuntu1404_5.5-54_amd64.deb

$ sudo dpkg -i cuda-repo-ubuntu1404_5.5-54_amd64.deb

$ cat /etc/apt/sources.list.d/cuda.list

deb http://developer.download.nvidia.com/compute/cuda/repos/ubuntu1404/x86_64 /

$ sudo apt-get update

<...>

```

**Note:** During the **apt-get update** command, there are several warnings for not found files, which can be safely ignored. For example:

```

W: Failed to fetch <...>/binary-ppc64el/Packages 404 Not Found [IP: <...>]

```

This warning happens as a result of the foreign-architecture setting combined with a different URL used for Ubuntu servers hosting ppc64el binary packages (that is, ports.ubuntu.com), at the time this publication was written.

Finally, install the cuda-cross-ppc64el meta-package, and the nvidia-nsight packages (Example 23 on page 31).

```

$ sudo apt-get install cuda-cross-ppc64el

<...>

The following NEW packages will be installed:

<...>

cuda-core-5-5-power8 cuda-cross-ppc64el cuda-cross-ppc64el-5-5-power8

<...>

Do you want to continue? [Y/n] y

WARNING: The following packages cannot be authenticated!

Install these packages without verification? [y/N] y

<...>

Setting up cuda-cross-ppc64el (5.5-54) ...

*** LICENSE AGREEMENT ***

$ sudo apt-get install nvidia-nsight

<...>

The following NEW packages will be installed:

nvidia-cuda-doc nvidia-nsight

Do you want to conitnue? [Y/n] y

```

For more information, refer to the Linux Getting Started Guide (also known as NVIDIA CUDA Getting Started Guide for Linux)  $\rightarrow$  Installing CUDA Development Tools  $\rightarrow$  Install the NVIDIA CUDA Toolkit Package  $\rightarrow$  Manager Installation  $\rightarrow$  Available packages:

http://developer.nvidia.com/cuda-downloads

# System monitoring

The nvidia-smi tool, which is provided by NVIDIA, is used to manage and monitor activities of the GPU devices. In Ubuntu 14.10, the nvidia-smi tool is included with the nvidia-340 DEB package. Because nvidia-smi has many options, the topic is only introduced in this section. It is recommended that you learn more about the nvidia-smi tool at the following site:

http://developer.nvidia.com/nvidia-system-management-interface

## Querying the state and properties of devices

Run **nvidia-smi** to show a summary of all GPUs attached to the system. Use **nvidia-smi** -**q** to display the current state and properties of the devices (Example 24). An individual device can be accessed with the -**i** <**id**> option, where < id> is the identification number of the card.

Example 24 nvidia-smi: displaying devices state with -q option (some output omitted)

```

$ sudo nvidia-smi -q

=========NVSMI LOG===========

Timestamp : Thu Nov 27 10:32:44 2014

Driver Version : 340.50

Attached GPUs : 2

```

```

GPU 0002:01:00.0

Product Name

: Tesla K40m

: Tesla

Product Brand

: Disabled

Display Mode

: Disabled

Display Active

Persistence Mode

: Disabled

: Disabled

Accounting Mode

: 128

Accounting Mode Buffer Size

Driver Model

Current

: N/A

Pending

: N/A

Serial Number

: 0324114015717

GPU UUID

: GPU-9c8168e0-dc96-678f-902f-3997a6f2dfc5

Minor Number

: 80.80.3E.00.01

VBIOS Version

MultiGPU Board

: No

Board ID

: 0x20100

Inforom Version

Image Version

: 2081.0202.01.04

OEM Object

: 1.1

: 3.0

ECC Object

Power Management Object

: N/A

GPU Operation Mode

Current

: N/A

Pending

: N/A

PCI

: 0x01

Bus

Device

: 0x00

Domain

: 0x0002

Device Id

: 0x102310DE

Bus Id

: 0002:01:00.0

: 0x097E10DE

Sub System Id

GPU Link Info

PCIe Generation

Max

: 3

: 3

Current

Link Width

Max

: 16x

Current

: 16x

Bridge Chip

: N/A

Type

Firmware

: N/A

: N/A

Fan Speed

Performance State

: P0

Clocks Throttle Reasons

: Not Active

Idle

Applications Clocks Setting: Active

: Not Active

SW Power Cap

HW Slowdown

: Not Active

Unknown

: Not Active

FB Memory Usage

Total

: 11519 MiB

Used

: 55 MiB

: 11464 MiB

Free

BAR1 Memory Usage

```

```

Total

: 16384 MiB

Used

: 2 MiB

Free

: 16382 MiB

: Default

Compute Mode

Utilization

: 0 %

Gpu

: 0 %

Memory

: 0 %

Encoder

: 0 %

Decoder

Ecc Mode

Current

: Enabled

: Enabled

Pending

ECC Errors

Volatile

Single Bit

Device Memory

: 0

Register File

: 0

L1 Cache

: 0

L2 Cache

: 0

Texture Memory

: 0

Total

: 0

Double Bit

: 0

Device Memory

Register File

: 0

L1 Cache

: 0

L2 Cache

: 0

Texture Memory

: 0

Total

: 0

Aggregate

Single Bit

: 0

Device Memory

Register File

: 0

L1 Cache

: 0

: 0

L2 Cache

Texture Memory

: 0

Total

: 0

Double Bit

Device Memory

: 0

Register File

: 0

L1 Cache

: 0

L2 Cache

: 0

: 0

Texture Memory

: 0

Total

Retired Pages

: 0

Single Bit ECC

Double Bit ECC

: 0

: No

Pending

Temperature

: 39 C

GPU Current Temp

: 95 C

GPU Shutdown Temp

GPU Slowdown Temp

: 90 C

Power Readings

: Supported

Power Management

Power Draw

: 63.16 W

Power Limit

: 235.00 W

```

Default Power Limit : 235.00 W

Enforced Power Limit : 235.00 W

Min Power Limit : 180.00 W

Max Power Limit : 235.00 W

Clocks

Graphics : 745 MHz

SM : 745 MHz

Memory : 3004 MHz

Applications Clocks

Graphics : 745 MHz

Memory : 3004 MHz

Default Applications Clocks

Graphics : 745 MHz

Memory : 3004 MHz

Max Clocks

Graphics : 875 MHz SM : 875 MHz Memory : 3004 MHz

Clock Policy

Auto Boost : N/A

Auto Boost Default : N/A

Compute Processes : None

GPU 0006:01:00.0

Product Name : Tesla K40m

Product Brand : Tesla

<... output omitted ...>

Query just one or more of the device properties by adding the **-d <property\_name>** option, where *property\_name* can assume the values that are shown in Table 2.

Table 2 nvidia-smi: query properties name

| Property         | Description                                                                         |

|------------------|-------------------------------------------------------------------------------------|

| MEMORY           | Show memory usage statistics                                                        |

| UTILIZATION      | Show utilization statistics of GPU, memory, encoder, and decoder subsystems         |

| ECC              | Show status of ECC and error statistics                                             |

| TEMPERATURE      | Display GPU temperature                                                             |

| POWER            | Show power management status                                                        |

| CLOCK            | Show clock rate of graphics, SM, memory, and applications; display usage statistics |

| SUPPORTED_CLOCKS | Display available combinations to GPU and memory clock boost                        |

| COMPUTE          | Display current compute mode                                                        |

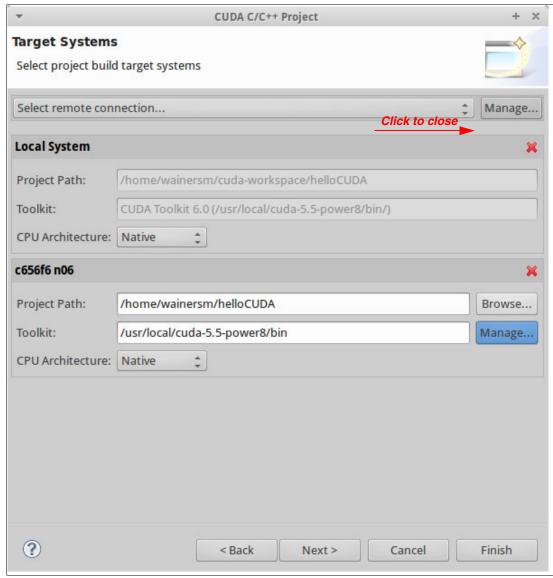

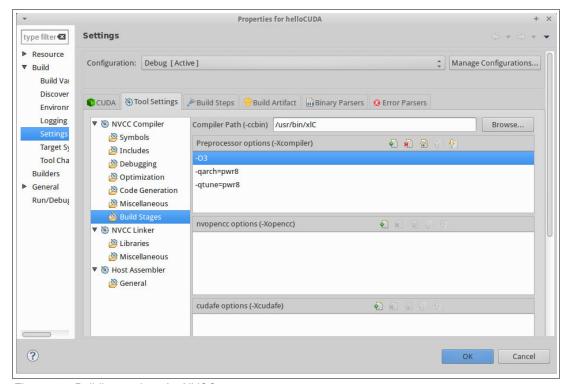

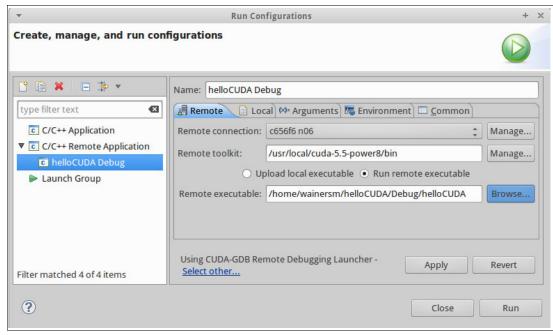

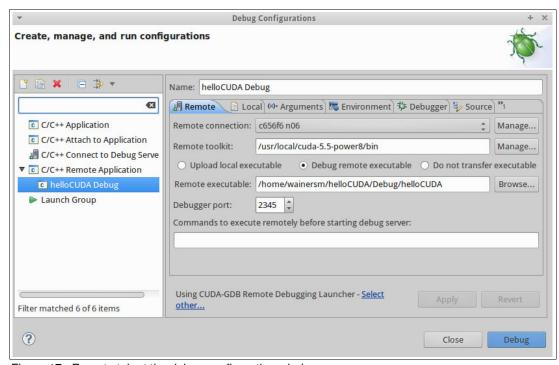

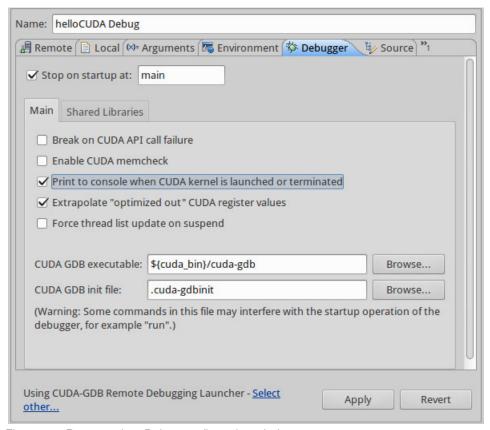

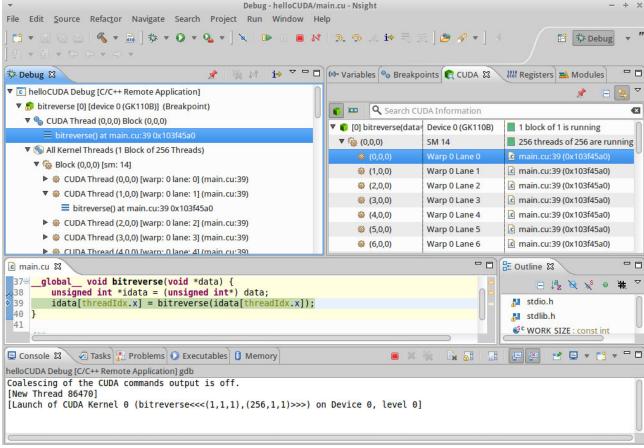

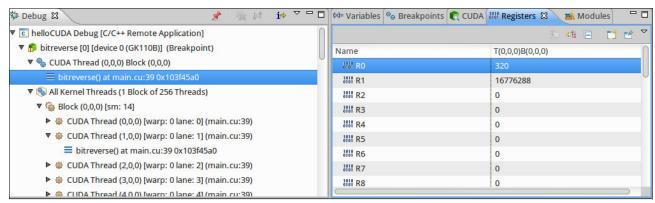

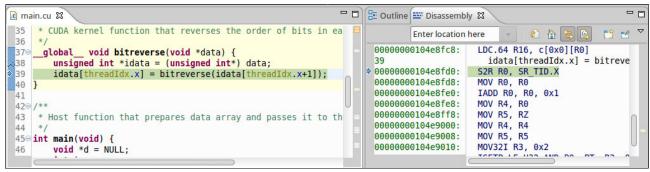

| PIDS             | List running applications                                                           |